Spectrum Signal Processing | Monaco Technical Reference |

| Registers |

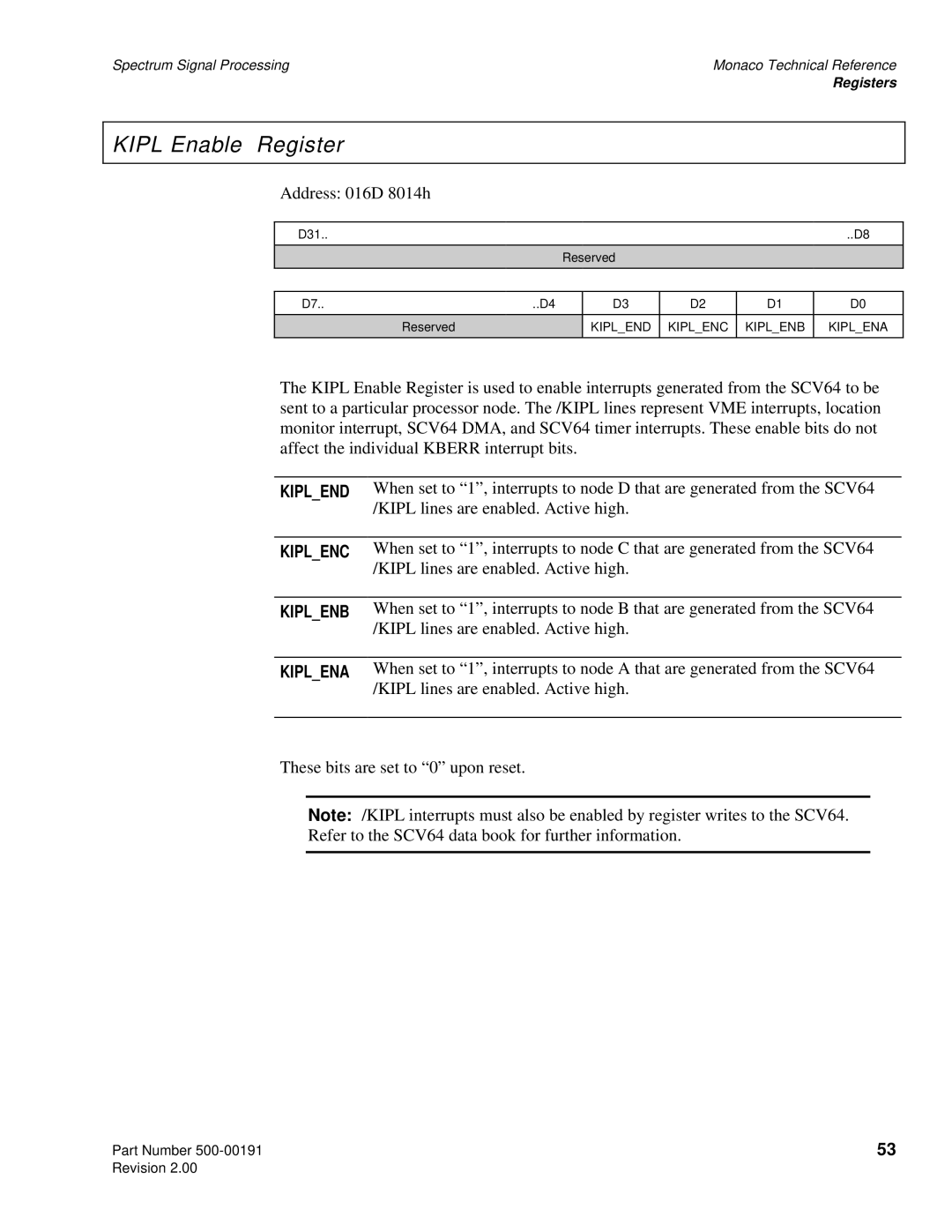

KIPL Enable Register

Address: 016D 8014h

D31.. |

|

|

|

|

| ..D8 |

|

|

|

|

|

|

|

|

| Reserved |

|

|

| |

|

|

|

|

|

|

|

D7.. | ..D4 |

| D3 | D2 | D1 | D0 |

|

|

|

|

|

|

|

Reserved |

|

| KIPL_END | KIPL_ENC | KIPL_ENB | KIPL_ENA |

|

|

|

|

|

|

|

The KIPL Enable Register is used to enable interrupts generated from the SCV64 to be sent to a particular processor node. The /KIPL lines represent VME interrupts, location monitor interrupt, SCV64 DMA, and SCV64 timer interrupts. These enable bits do not affect the individual KBERR interrupt bits.

KIPL_END | When set to “1”, interrupts to node D that are generated from the SCV64 |

| /KIPL lines are enabled. Active high. |

|

|

KIPL_ENC | When set to “1”, interrupts to node C that are generated from the SCV64 |

| /KIPL lines are enabled. Active high. |

|

|

KIPL_ENB | When set to “1”, interrupts to node B that are generated from the SCV64 |

| /KIPL lines are enabled. Active high. |

|

|

KIPL_ENA | When set to “1”, interrupts to node A that are generated from the SCV64 |

| /KIPL lines are enabled. Active high. |

|

|

These bits are set to “0” upon reset.

Note: /KIPL interrupts must also be enabled by register writes to the SCV64.

Refer to the SCV64 data book for further information.

Part Number | 53 |

Revision 2.00 |

|