UltraSPARC T2 | 1.2 | |

GHz | ||

|

|

|

| 64 | |

SPARC |

| L2 |

| |

core |

| Bank 0 |

| |

|

|

| 128 | |

SPARC |

| L2 |

| |

core |

| Bank 1 | 64 | |

|

|

| ||

|

|

| 64 | |

SPARC |

| L2 |

| |

core |

| Bank 0 |

| |

|

|

| 128 | |

SPARC |

| L2 |

| |

core | Cache | Bank 1 | 64 | |

|

| |||

| Crossbar |

| 64 | |

SPARC | (CCX) | L2 | ||

| ||||

core |

| Bank 0 |

| |

|

|

| 128 | |

SPARC |

| L2 |

| |

core |

| Bank 1 | 64 | |

|

|

| ||

SPARC |

| L2 | 64 | |

|

| |||

core |

| Bank 0 |

| |

|

|

| 128 | |

SPARC |

| L2 |

| |

core |

| Bank 1 | 64 | |

|

|

| ||

TCU | CCU | Efuse |

| |

10 Gb MAC |

| SIU | ||

| NIU |

| ||

10 Gb MAC |

|

| ||

|

| SSI ROM I/F | ||

667

MHz

MCU0

MCU1

MCU2

MCU3

Fully buffered

4.0DIMMs (FBD)

GHz

10

14

10

14

10

14

10

14

10

14

10

14

10

14

10

14

Optional dual channel mode

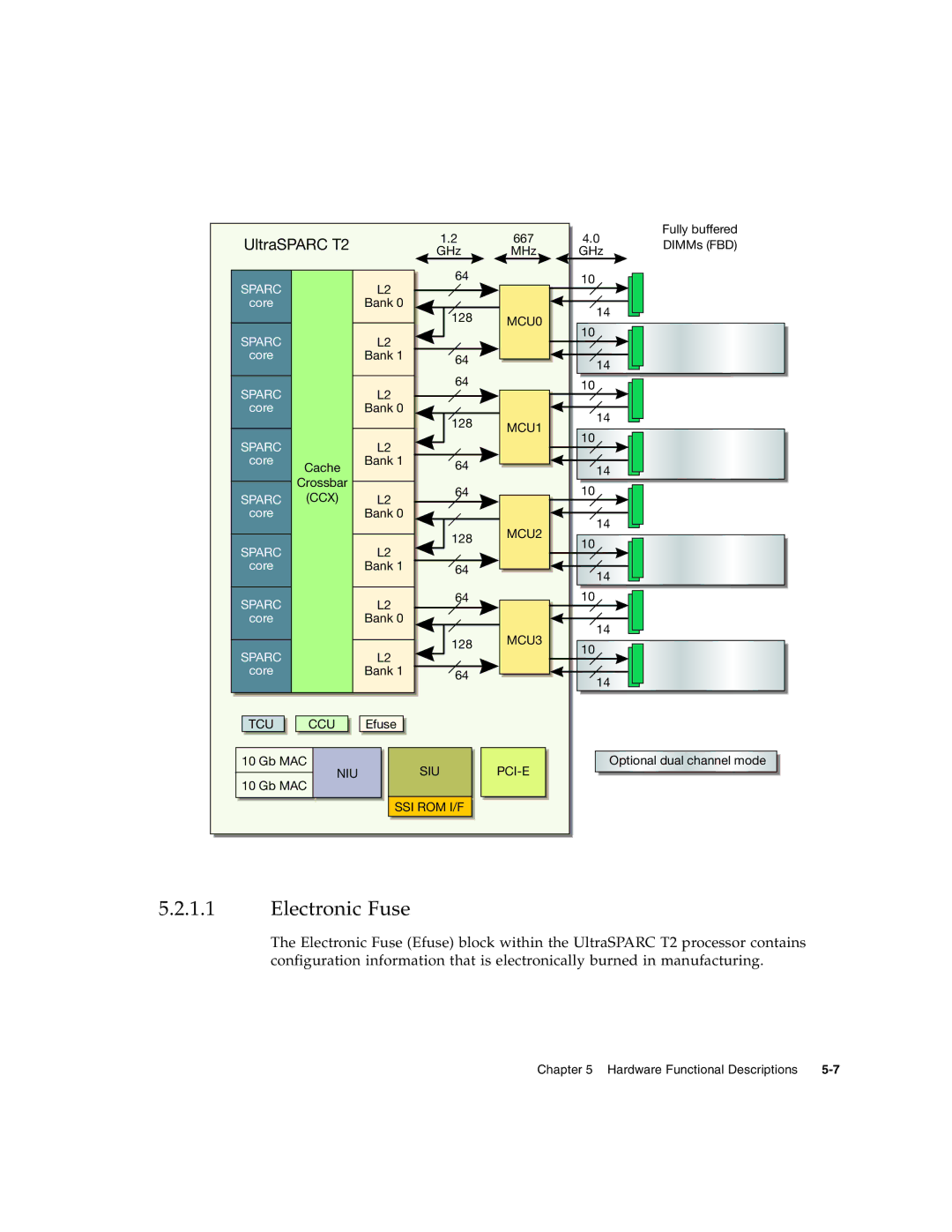

5.2.1.1Electronic Fuse

The Electronic Fuse (Efuse) block within the UltraSPARC T2 processor contains configuration information that is electronically burned in manufacturing.

Chapter 5 Hardware Functional Descriptions |