Detailed Description

References

See the following websites for more

•http://www.xilinx.com/products/ipcenter/V6_PCI_Express_Block.htm

•

In addition, see the PCI Express specifications for more information. [Ref 27]

10. SFP Module Connector

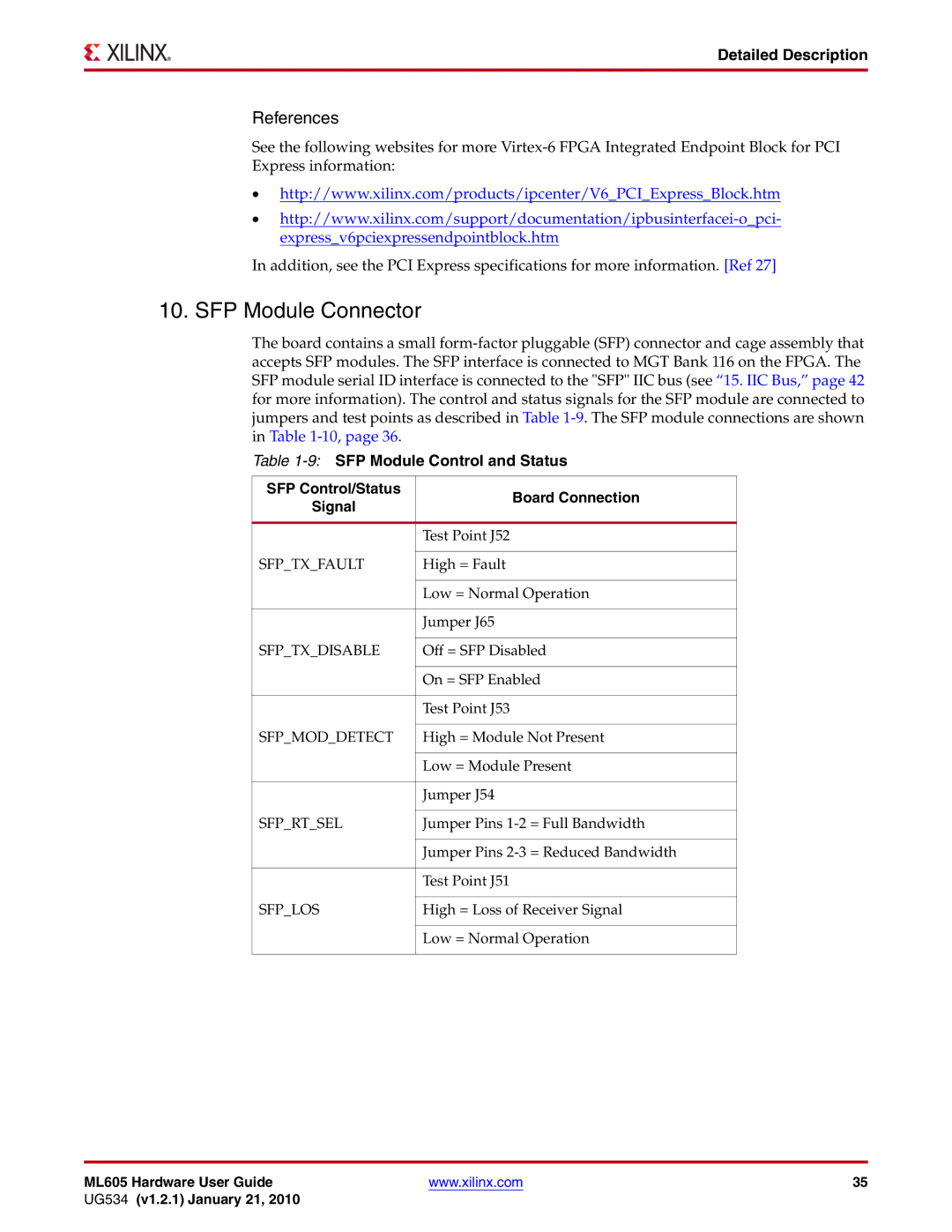

The board contains a small

Table

SFP Control/Status | Board Connection | |

Signal | ||

| ||

|

| |

| Test Point J52 | |

|

| |

SFP_TX_FAULT | High = Fault | |

|

| |

| Low = Normal Operation | |

|

| |

| Jumper J65 | |

|

| |

SFP_TX_DISABLE | Off = SFP Disabled | |

|

| |

| On = SFP Enabled | |

|

| |

| Test Point J53 | |

|

| |

SFP_MOD_DETECT | High = Module Not Present | |

|

| |

| Low = Module Present | |

|

| |

| Jumper J54 | |

|

| |

SFP_RT_SEL | Jumper Pins | |

|

| |

| Jumper Pins | |

|

| |

| Test Point J51 | |

|

| |

SFP_LOS | High = Loss of Receiver Signal | |

|

| |

| Low = Normal Operation | |

|

|

ML605 Hardware User Guide | www.xilinx.com | 35 |

UG534 (v1.2.1) January 21, 2010 |

|

|