Detailed Description

8. Multi-Gigabit Transceivers (GTX MGTs)

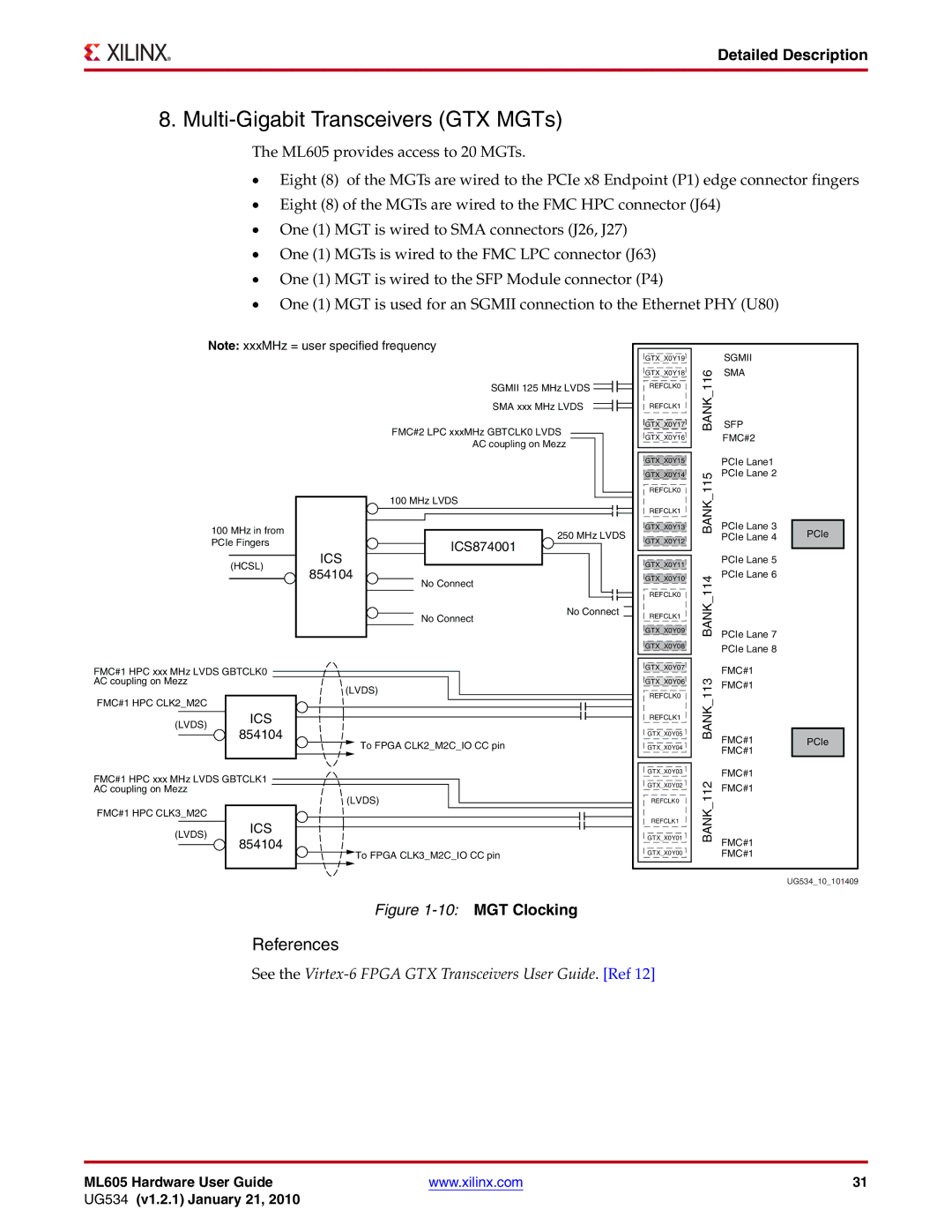

The ML605 provides access to 20 MGTs.

•Eight (8) of the MGTs are wired to the PCIe x8 Endpoint (P1) edge connector fingers

•Eight (8) of the MGTs are wired to the FMC HPC connector (J64)

•One (1) MGT is wired to SMA connectors (J26, J27)

•One (1) MGTs is wired to the FMC LPC connector (J63)

•One (1) MGT is wired to the SFP Module connector (P4)

•One (1) MGT is used for an SGMII connection to the Ethernet PHY (U80)

Note: xxxMHz = user specified frequency

GTX_X0Y19 GTX_X0Y18

116

SGMII

SMA

100 MHz in from PCIe Fingers

(HCSL)

ICS

854104

SGMII 125 MHz LVDS ![]()

![]()

SMA xxx MHz LVDS

FMC#2 LPC xxxMHz GBTCLK0 LVDS

AC coupling on Mezz

100 MHz LVDS

250 MHz LVDS

ICS874001

REFCLK0

REFCLK1

GTX_X0Y17 GTX_X0Y16

GTX_X0Y15 GTX_X0Y14

REFCLK0

REFCLK1

GTX_X0Y13 GTX_X0Y12

GTX_X0Y11 GTX_X0Y10

BANK_115 BANK_

SFP

FMC#2

PCIe Lane1 PCIe Lane 2

PCIe Lane 3 PCIe Lane 4

PCIe Lane 5

PCIe Lane 6

PCIe

No Connect

No Connect

No Connect

REFCLK0

REFCLK1

GTX_X0Y09

GTX_X0Y08

BANK_114

PCIe Lane 7

PCIe Lane 8

FMC#1 HPC xxx MHz LVDS GBTCLK0 AC coupling on Mezz

(LVDS)

FMC#1 HPC CLK2_M2C

(LVDS) | ICS | ||

854104 | |||

|

| ||

|

| ||

![]() To FPGA CLK2_M2C_IO CC pin

To FPGA CLK2_M2C_IO CC pin

FMC#1 HPC xxx MHz LVDS GBTCLK1 AC coupling on Mezz

(LVDS)

FMC#1 HPC CLK3_M2C

(LVDS) | ICS | ||

854104 | |||

|

| ||

|

| ||

To FPGA CLK3_M2C_IO CC pin

To FPGA CLK3_M2C_IO CC pin

GTX_X0Y07 GTX_X0Y06

REFCLK0

REFCLK1

GTX_X0Y05 GTX_X0Y04

GTX_X0Y03 GTX_X0Y02

REFCLK0

REFCLK1

GTX_X0Y01

GTX_X0Y00

BANK_112 BANK_113

FMC#1

FMC#1

FMC#1

FMC#1

FMC#1

FMC#1

FMC#1

FMC#1

PCIe

UG534_10_101409

Figure 1-10: MGT Clocking

References

See the

ML605 Hardware User Guide | www.xilinx.com | 31 |

UG534 (v1.2.1) January 21, 2010 |

|

|