Chapter 1: ML605 Evaluation Board

Table

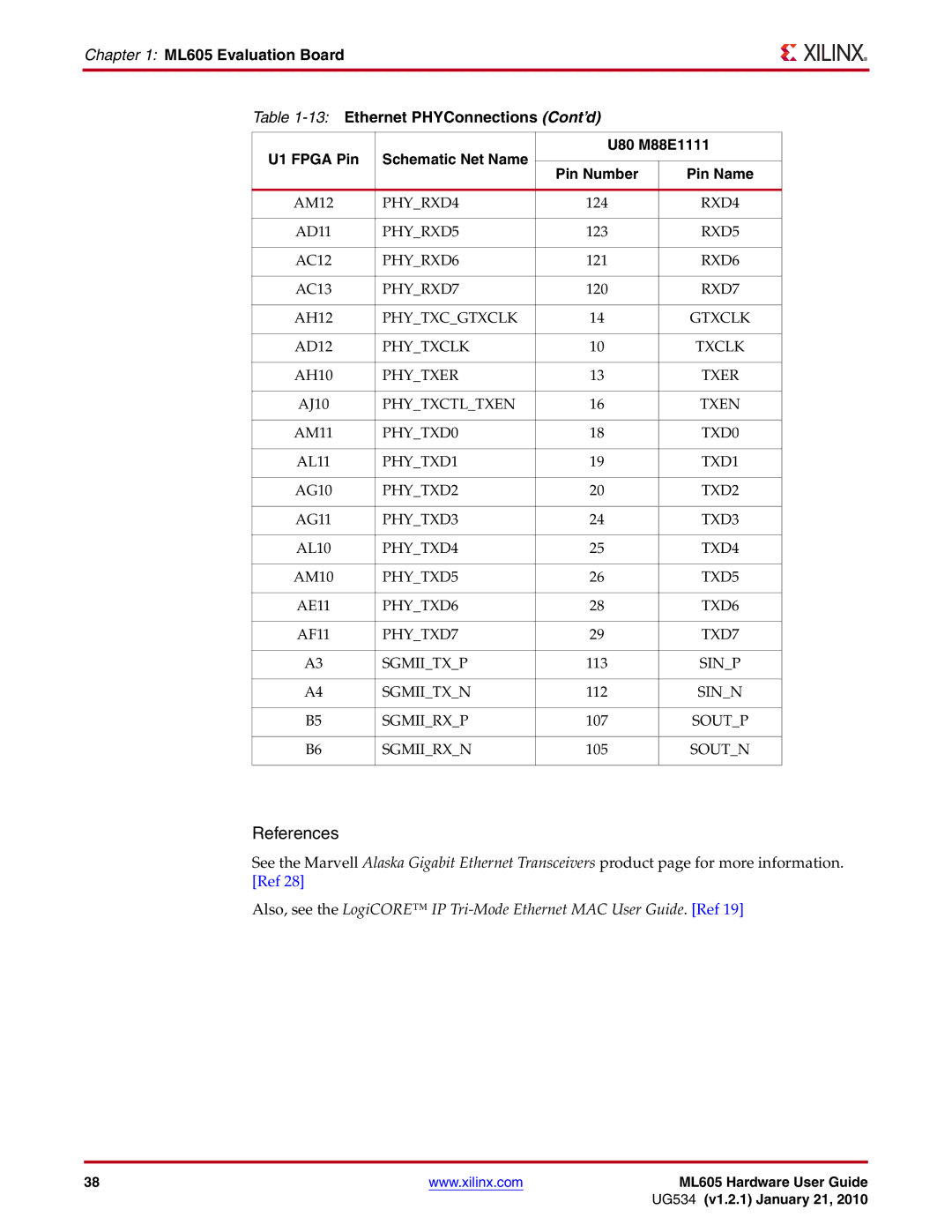

U1 FPGA Pin | Schematic Net Name | U80 M88E1111 | ||

|

| |||

Pin Number | Pin Name | |||

|

| |||

|

|

|

| |

AM12 | PHY_RXD4 | 124 | RXD4 | |

|

|

|

| |

AD11 | PHY_RXD5 | 123 | RXD5 | |

|

|

|

| |

AC12 | PHY_RXD6 | 121 | RXD6 | |

|

|

|

| |

AC13 | PHY_RXD7 | 120 | RXD7 | |

|

|

|

| |

AH12 | PHY_TXC_GTXCLK | 14 | GTXCLK | |

|

|

|

| |

AD12 | PHY_TXCLK | 10 | TXCLK | |

|

|

|

| |

AH10 | PHY_TXER | 13 | TXER | |

|

|

|

| |

AJ10 | PHY_TXCTL_TXEN | 16 | TXEN | |

|

|

|

| |

AM11 | PHY_TXD0 | 18 | TXD0 | |

|

|

|

| |

AL11 | PHY_TXD1 | 19 | TXD1 | |

|

|

|

| |

AG10 | PHY_TXD2 | 20 | TXD2 | |

|

|

|

| |

AG11 | PHY_TXD3 | 24 | TXD3 | |

|

|

|

| |

AL10 | PHY_TXD4 | 25 | TXD4 | |

|

|

|

| |

AM10 | PHY_TXD5 | 26 | TXD5 | |

|

|

|

| |

AE11 | PHY_TXD6 | 28 | TXD6 | |

|

|

|

| |

AF11 | PHY_TXD7 | 29 | TXD7 | |

|

|

|

| |

A3 | SGMII_TX_P | 113 | SIN_P | |

|

|

|

| |

A4 | SGMII_TX_N | 112 | SIN_N | |

|

|

|

| |

B5 | SGMII_RX_P | 107 | SOUT_P | |

|

|

|

| |

B6 | SGMII_RX_N | 105 | SOUT_N | |

|

|

|

| |

References

See the Marvell Alaska Gigabit Ethernet Transceivers product page for more information. [Ref 28]

Also, see the LogiCORE™ IP

38 | www.xilinx.com | ML605 Hardware User Guide |

|

| UG534 (v1.2.1) January 21, 2010 |