|

|

|

|

|

| Detailed Description | |

|

|

|

|

|

|

|

|

|

|

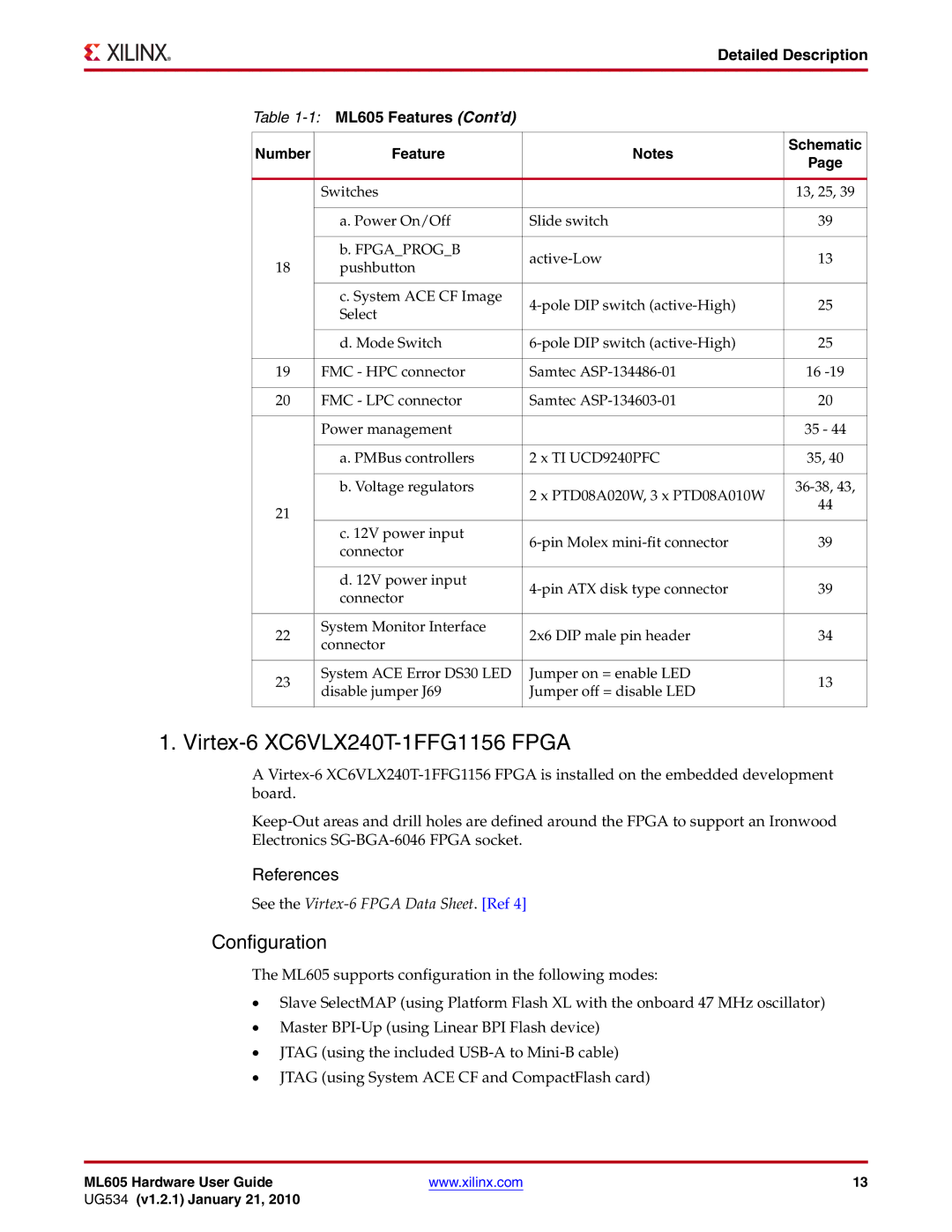

| Table | ML605 Features (Cont’d) |

|

| |

|

|

|

|

|

|

|

|

|

|

| Number |

| Feature | Notes | Schematic |

|

|

|

| Page | |||

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| Switches |

| 13, 25, 39 |

|

|

|

|

|

|

|

|

|

|

|

|

| a. Power On/Off | Slide switch | 39 |

|

|

|

|

|

|

|

|

|

|

|

|

| b. FPGA_PROG_B | 13 | |

|

|

| 18 |

| pushbutton | ||

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

| c. System ACE CF Image | 25 | |

|

|

|

|

| Select | ||

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| d. Mode Switch | 25 | |

|

|

|

|

|

| ||

|

|

| 19 |

| FMC - HPC connector | Samtec | 16 |

|

|

|

|

|

| ||

|

|

| 20 |

| FMC - LPC connector | Samtec | 20 |

|

|

|

|

|

|

|

|

|

|

|

|

| Power management |

| 35 - 44 |

|

|

|

|

|

|

|

|

|

|

|

|

| a. PMBus controllers | 2 x TI UCD9240PFC | 35, 40 |

|

|

|

|

|

|

|

|

|

|

|

|

| b. Voltage regulators | 2 x PTD08A020W, 3 x PTD08A010W | |

|

|

|

|

|

| 44 | |

|

|

| 21 |

|

|

| |

|

|

|

|

| |||

|

|

|

|

| c. 12V power input | 39 | |

|

|

|

|

| connector | ||

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| d. 12V power input | 39 | |

|

|

|

|

| connector | ||

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| 22 |

| System Monitor Interface | 2x6 DIP male pin header | 34 |

|

| connector | |||||

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| 23 |

| System ACE Error DS30 LED | Jumper on = enable LED | 13 |

|

| disable jumper J69 | Jumper off = disable LED | ||||

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

1. Virtex-6 XC6VLX240T-1FFG1156 FPGA

A

Electronics

References

See the

Configuration

The ML605 supports configuration in the following modes:

•Slave SelectMAP (using Platform Flash XL with the onboard 47 MHz oscillator)

•Master

•JTAG (using the included

•JTAG (using System ACE CF and CompactFlash card)

ML605 Hardware User Guide | www.xilinx.com | 13 |

UG534 (v1.2.1) January 21, 2010 |

|

|