Chapter 1: ML605 Evaluation Board

Table

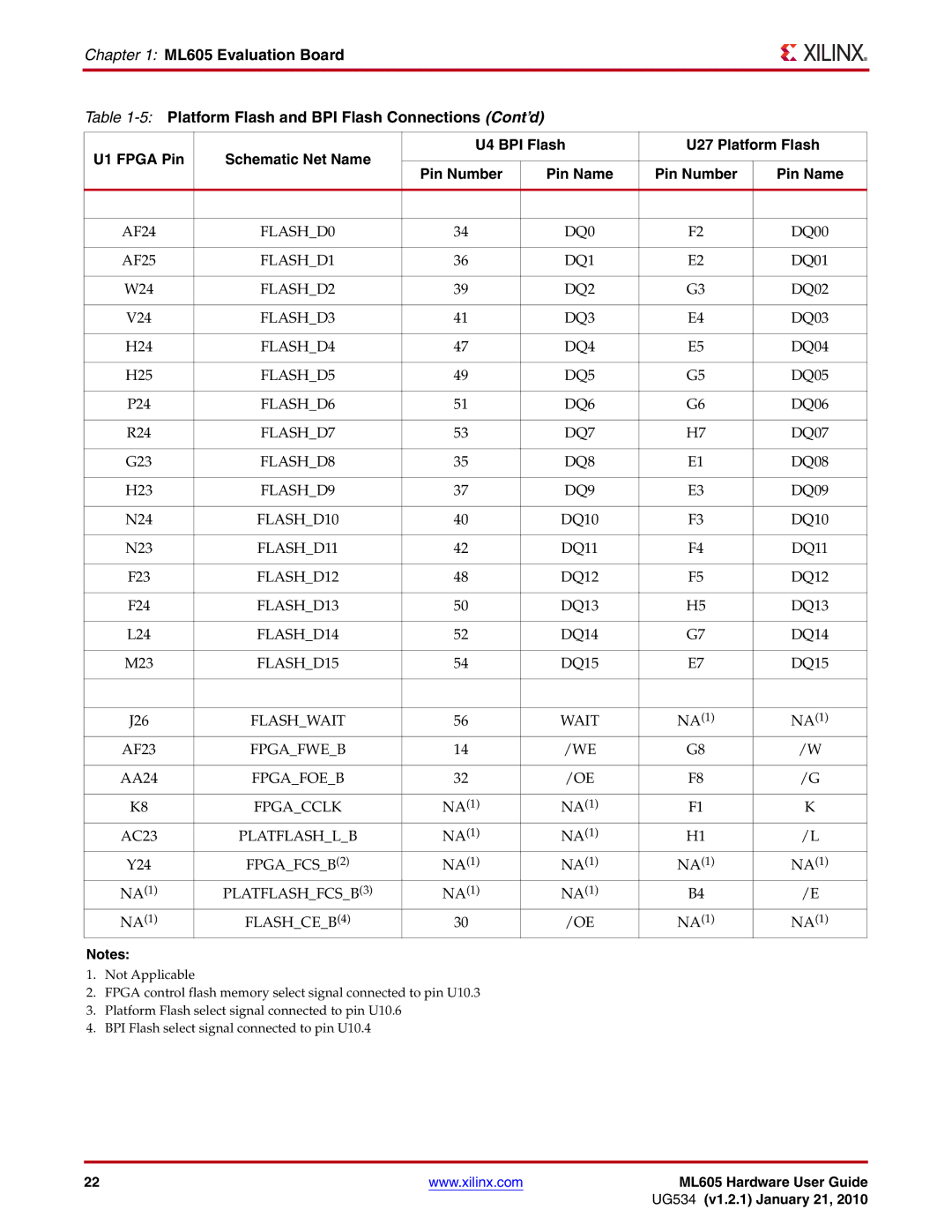

U1 FPGA Pin | Schematic Net Name | U4 BPI Flash | U27 Platform Flash | |||

|

|

|

| |||

Pin Number | Pin Name | Pin Number | Pin Name | |||

|

| |||||

|

|

|

|

|

| |

|

|

|

|

|

| |

AF24 | FLASH_D0 | 34 | DQ0 | F2 | DQ00 | |

|

|

|

|

|

| |

AF25 | FLASH_D1 | 36 | DQ1 | E2 | DQ01 | |

|

|

|

|

|

| |

W24 | FLASH_D2 | 39 | DQ2 | G3 | DQ02 | |

|

|

|

|

|

| |

V24 | FLASH_D3 | 41 | DQ3 | E4 | DQ03 | |

|

|

|

|

|

| |

H24 | FLASH_D4 | 47 | DQ4 | E5 | DQ04 | |

|

|

|

|

|

| |

H25 | FLASH_D5 | 49 | DQ5 | G5 | DQ05 | |

|

|

|

|

|

| |

P24 | FLASH_D6 | 51 | DQ6 | G6 | DQ06 | |

|

|

|

|

|

| |

R24 | FLASH_D7 | 53 | DQ7 | H7 | DQ07 | |

|

|

|

|

|

| |

G23 | FLASH_D8 | 35 | DQ8 | E1 | DQ08 | |

|

|

|

|

|

| |

H23 | FLASH_D9 | 37 | DQ9 | E3 | DQ09 | |

|

|

|

|

|

| |

N24 | FLASH_D10 | 40 | DQ10 | F3 | DQ10 | |

|

|

|

|

|

| |

N23 | FLASH_D11 | 42 | DQ11 | F4 | DQ11 | |

|

|

|

|

|

| |

F23 | FLASH_D12 | 48 | DQ12 | F5 | DQ12 | |

|

|

|

|

|

| |

F24 | FLASH_D13 | 50 | DQ13 | H5 | DQ13 | |

|

|

|

|

|

| |

L24 | FLASH_D14 | 52 | DQ14 | G7 | DQ14 | |

|

|

|

|

|

| |

M23 | FLASH_D15 | 54 | DQ15 | E7 | DQ15 | |

|

|

|

|

|

| |

|

|

|

|

|

| |

J26 | FLASH_WAIT | 56 | WAIT | NA(1) | NA(1) | |

AF23 | FPGA_FWE_B | 14 | /WE | G8 | /W | |

|

|

|

|

|

| |

AA24 | FPGA_FOE_B | 32 | /OE | F8 | /G | |

|

|

|

|

|

| |

K8 | FPGA_CCLK | NA(1) | NA(1) | F1 | K | |

AC23 | PLATFLASH_L_B | NA(1) | NA(1) | H1 | /L | |

Y24 | FPGA_FCS_B(2) | NA(1) | NA(1) | NA(1) | NA(1) | |

NA(1) | PLATFLASH_FCS_B(3) | NA(1) | NA(1) | B4 | /E | |

NA(1) | FLASH_CE_B(4) | 30 | /OE | NA(1) | NA(1) | |

Notes:

1.Not Applicable

2.FPGA control flash memory select signal connected to pin U10.3

3.Platform Flash select signal connected to pin U10.6

4.BPI Flash select signal connected to pin U10.4

22 | www.xilinx.com | ML605 Hardware User Guide |

|

| UG534 (v1.2.1) January 21, 2010 |