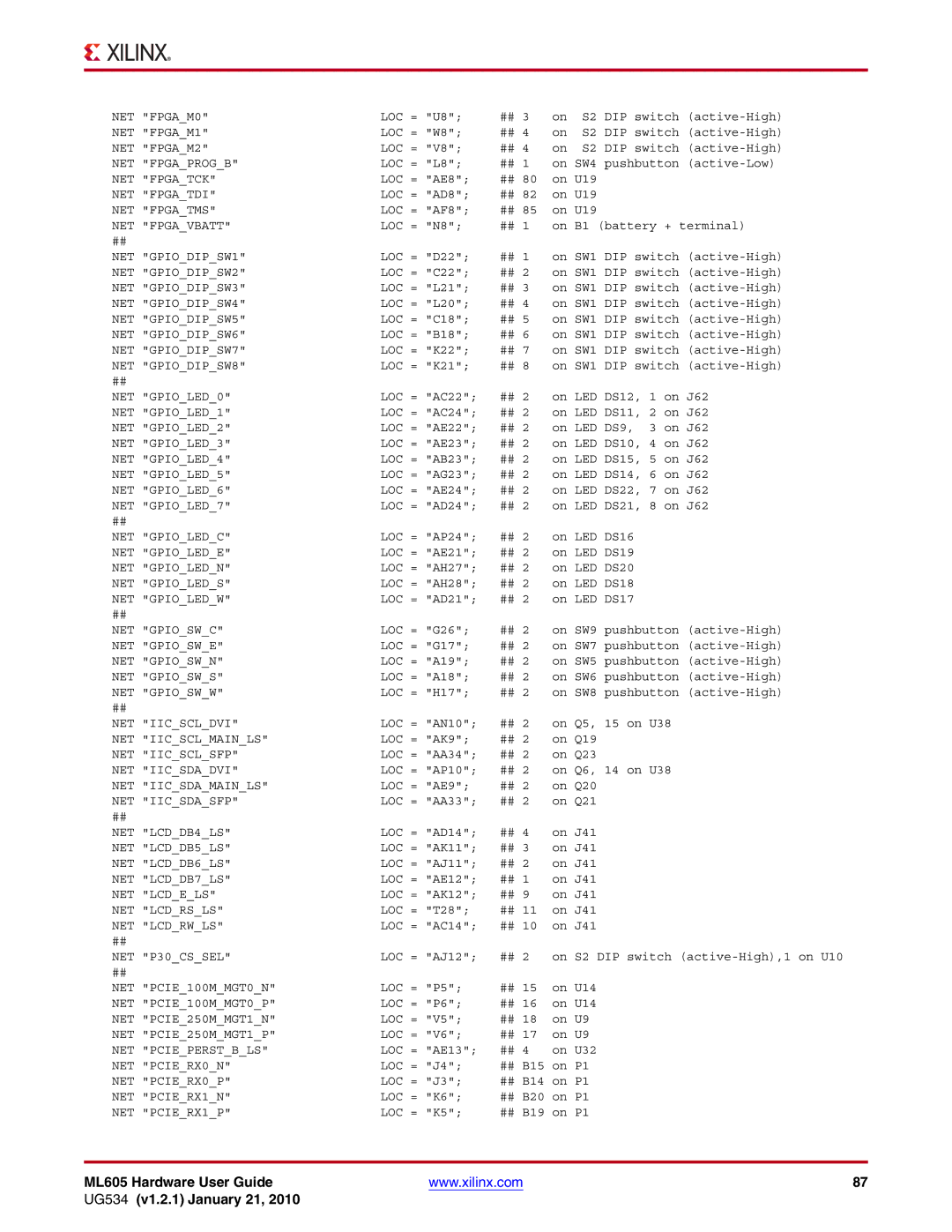

NET "FPGA_M0"

NET "FPGA_M1"

NET "FPGA_M2"

NET "FPGA_PROG_B" NET "FPGA_TCK" NET "FPGA_TDI" NET "FPGA_TMS" NET "FPGA_VBATT"

##

NET "GPIO_DIP_SW1" NET "GPIO_DIP_SW2" NET "GPIO_DIP_SW3" NET "GPIO_DIP_SW4" NET "GPIO_DIP_SW5" NET "GPIO_DIP_SW6" NET "GPIO_DIP_SW7" NET "GPIO_DIP_SW8"

##

NET "GPIO_LED_0"

NET "GPIO_LED_1"

NET "GPIO_LED_2"

NET "GPIO_LED_3"

NET "GPIO_LED_4"

NET "GPIO_LED_5"

NET "GPIO_LED_6"

NET "GPIO_LED_7"

##

NET "GPIO_LED_C"

NET "GPIO_LED_E"

NET "GPIO_LED_N"

NET "GPIO_LED_S"

NET "GPIO_LED_W"

##

NET "GPIO_SW_C"

NET "GPIO_SW_E"

NET "GPIO_SW_N"

NET "GPIO_SW_S"

NET "GPIO_SW_W"

##

NET "IIC_SCL_DVI"

NET "IIC_SCL_MAIN_LS" NET "IIC_SCL_SFP"

NET "IIC_SDA_DVI"

NET "IIC_SDA_MAIN_LS" NET "IIC_SDA_SFP"

##

NET "LCD_DB4_LS"

NET "LCD_DB5_LS"

NET "LCD_DB6_LS"

NET "LCD_DB7_LS" NET "LCD_E_LS" NET "LCD_RS_LS" NET "LCD_RW_LS"

##

NET "P30_CS_SEL"

##

NET "PCIE_100M_MGT0_N" NET "PCIE_100M_MGT0_P" NET "PCIE_250M_MGT1_N" NET "PCIE_250M_MGT1_P" NET "PCIE_PERST_B_LS"

NET "PCIE_RX0_N"

NET "PCIE_RX0_P"

NET "PCIE_RX1_N"

NET "PCIE_RX1_P"

LOC = "U8"; LOC = "W8"; LOC = "V8"; LOC = "L8"; LOC = "AE8"; LOC = "AD8"; LOC = "AF8"; LOC = "N8";

LOC = "D22"; LOC = "C22"; LOC = "L21"; LOC = "L20"; LOC = "C18"; LOC = "B18"; LOC = "K22"; LOC = "K21";

LOC = "AC22"; LOC = "AC24"; LOC = "AE22"; LOC = "AE23"; LOC = "AB23"; LOC = "AG23"; LOC = "AE24"; LOC = "AD24";

LOC = "AP24"; LOC = "AE21"; LOC = "AH27"; LOC = "AH28"; LOC = "AD21";

LOC = "G26"; LOC = "G17"; LOC = "A19"; LOC = "A18"; LOC = "H17";

LOC = "AN10"; LOC = "AK9"; LOC = "AA34"; LOC = "AP10"; LOC = "AE9"; LOC = "AA33";

LOC = "AD14"; LOC = "AK11"; LOC = "AJ11"; LOC = "AE12"; LOC = "AK12"; LOC = "T28"; LOC = "AC14";

LOC = "AJ12";

LOC = "P5"; LOC = "P6"; LOC = "V5"; LOC = "V6"; LOC = "AE13"; LOC = "J4"; LOC = "J3"; LOC = "K6"; LOC = "K5";

## 3 | on | S2 | DIP switch | |||

## | 4 | on | S2 | DIP | switch | |

## | 4 | on | S2 | DIP | switch | |

##1 on SW4 pushbutton

##80 on U19

##82 on U19

##85 on U19

##1 on B1 (battery + terminal)

##1 on SW1 DIP switch

##2 on SW1 DIP switch

##3 on SW1 DIP switch

##4 on SW1 DIP switch

##5 on SW1 DIP switch

##6 on SW1 DIP switch

##7 on SW1 DIP switch

##8 on SW1 DIP switch

##2 on LED DS12, 1 on J62

##2 on LED DS11, 2 on J62

## 2 on LED DS9, 3 on J62

##2 on LED DS10, 4 on J62

##2 on LED DS15, 5 on J62

##2 on LED DS14, 6 on J62

##2 on LED DS22, 7 on J62

##2 on LED DS21, 8 on J62

##2 on LED DS16

##2 on LED DS19

##2 on LED DS20

##2 on LED DS18

##2 on LED DS17

##2 on SW9 pushbutton

##2 on SW7 pushbutton

##2 on SW5 pushbutton

##2 on SW6 pushbutton

##2 on SW8 pushbutton

##2 on Q5, 15 on U38

##2 on Q19

##2 on Q23

##2 on Q6, 14 on U38

##2 on Q20

##2 on Q21

##4 on J41

##3 on J41

##2 on J41

##1 on J41

##9 on J41

##11 on J41

##10 on J41

##2 on S2 DIP switch

##15 on U14

##16 on U14

##18 on U9

##17 on U9

##4 on U32

##B15 on P1

##B14 on P1

##B20 on P1

##B19 on P1

ML605 Hardware User Guide | www.xilinx.com | 87 |

UG534 (v1.2.1) January 21, 2010 |

|

|