Chapter 1: ML605 Evaluation Board

FPGA Power Supply Margining

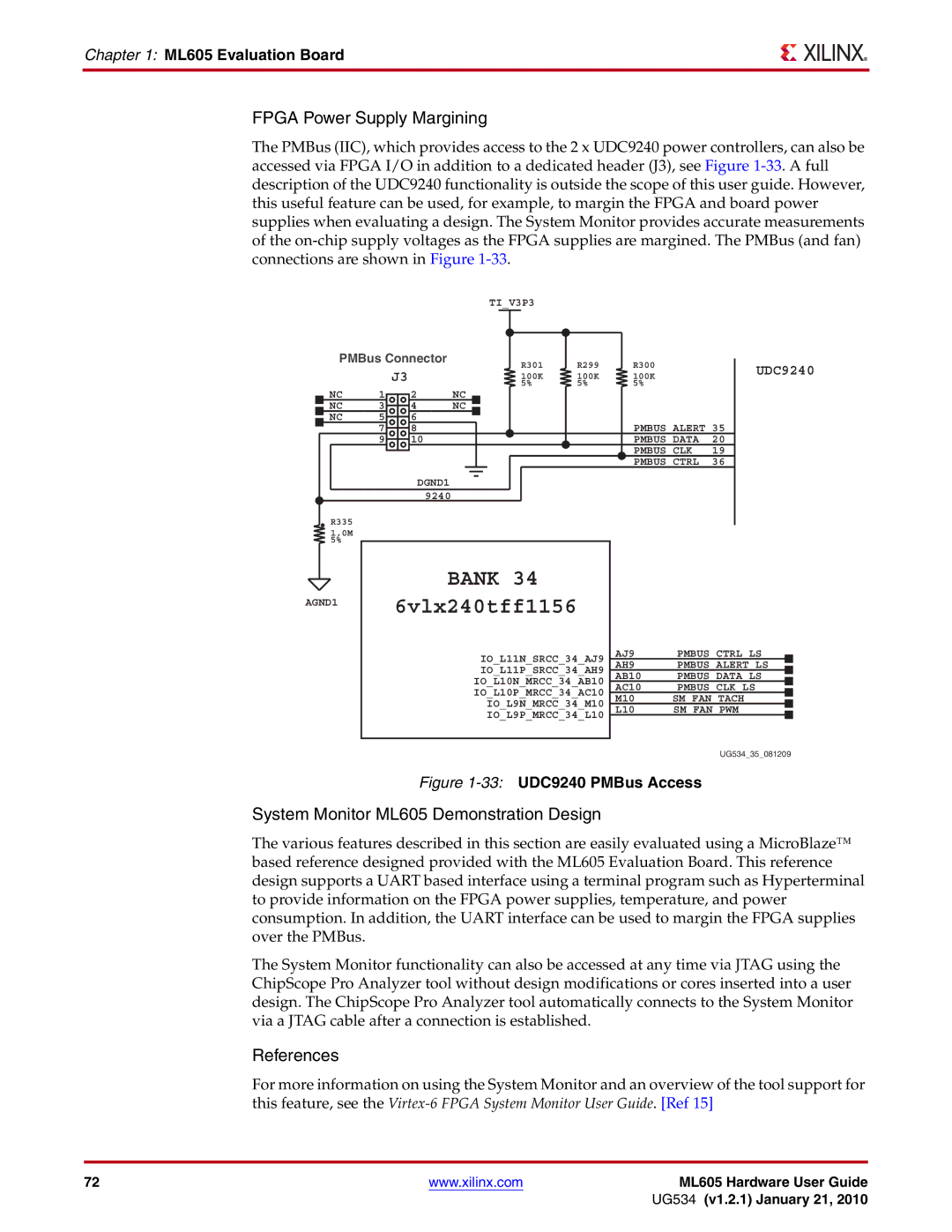

The PMBus (IIC), which provides access to the 2 x UDC9240 power controllers, can also be accessed via FPGA I/O in addition to a dedicated header (J3), see Figure

TI_V3P3

PMBus Connector | R301 | R299 | ||

| J3 |

| ||

|

| 100K | 100K | |

|

|

| 5% | 5% |

NC | 1 | 2 | NC |

|

NC | 3 | 4 | NC |

|

NC | 5 | 6 |

|

|

78

910

DGND1

9240

R300 | UDC9240 |

100K | |

5% |

|

PMBUS_ALERT 35

PMBUS_DATA 20

PMBUS_CLK 19

PMBUS_CTRL 36

R335

1.0M

5%

AGND1

BANK 34

6vlx240tff1156

IO_L11N_SRCC_34_AJ9

IO_L11P_SRCC_34_AH9

IO_L10N_MRCC_34_AB10

IO_L10P_MRCC_34_AC10

IO_L9N_MRCC_34_M10

IO_L9P_MRCC_34_L10

AJ9 | PMBUS_CTRL_LS |

|

AH9 | PMBUS_ALERT_LS |

|

AB10 | PMBUS_DATA_LS |

|

AC10 | PMBUS_CLK_LS |

|

M10 | SM_FAN_TACH |

|

L10 | SM_FAN_PWM |

|

|

|

|

UG534_35_081209

Figure 1-33: UDC9240 PMBus Access

System Monitor ML605 Demonstration Design

The various features described in this section are easily evaluated using a MicroBlaze™ based reference designed provided with the ML605 Evaluation Board. This reference design supports a UART based interface using a terminal program such as Hyperterminal to provide information on the FPGA power supplies, temperature, and power consumption. In addition, the UART interface can be used to margin the FPGA supplies over the PMBus.

The System Monitor functionality can also be accessed at any time via JTAG using the ChipScope Pro Analyzer tool without design modifications or cores inserted into a user design. The ChipScope Pro Analyzer tool automatically connects to the System Monitor via a JTAG cable after a connection is established.

References

For more information on using the System Monitor and an overview of the tool support for this feature, see the

72 | www.xilinx.com | ML605 Hardware User Guide |

|

| UG534 (v1.2.1) January 21, 2010 |