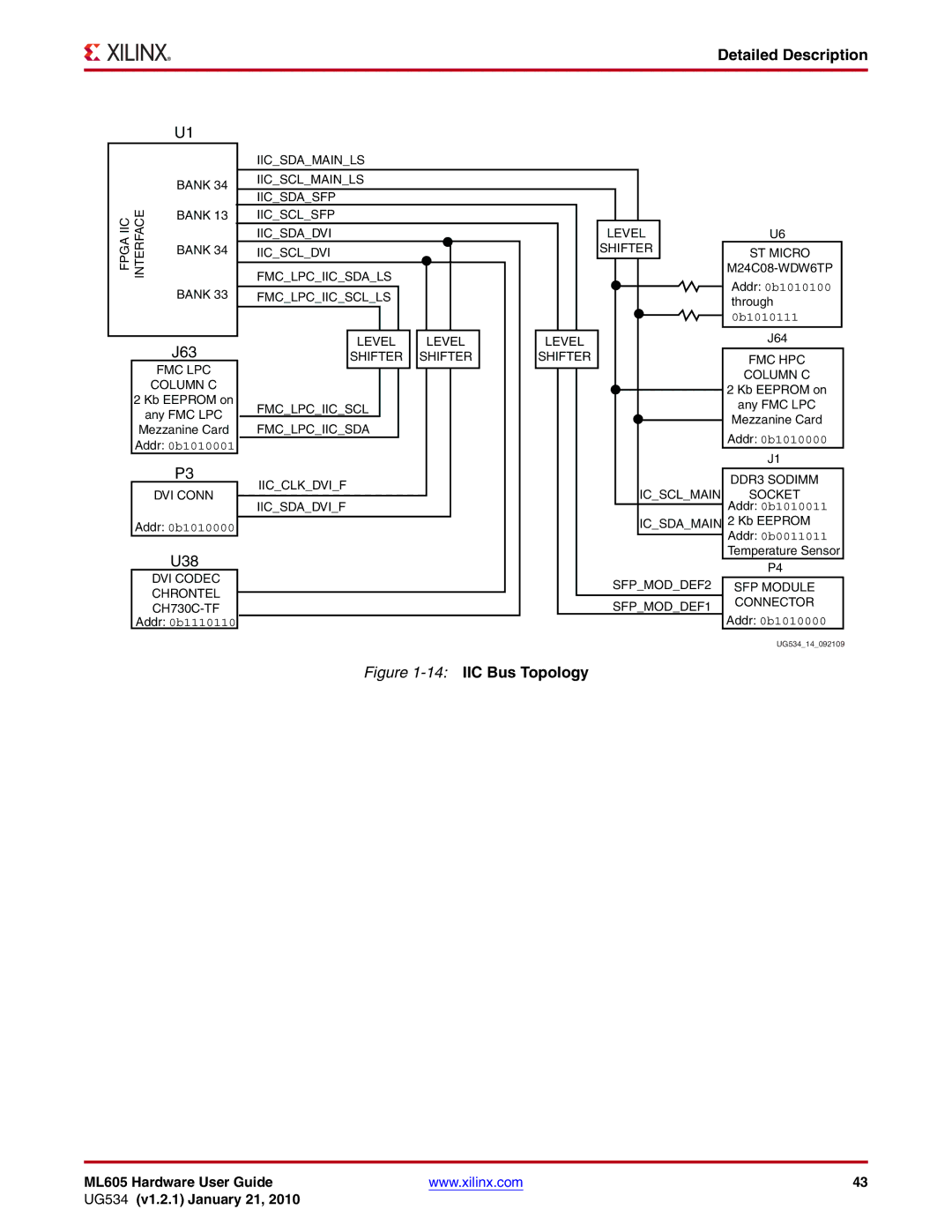

Detailed Description

U1

BANK 34 |

IIC_SDA_MAIN_LS IIC_SCL_MAIN_LS IIC_SDA_SFP

FPGA IIC INTERFACE | BANK 13 |

BANK 34 | |

| |

| BANK 33 |

J63

FMC LPC

COLUMN C

2 Kb EEPROM on

any FMC LPC

Mezzanine Card Addr: 0b1010001

P3

DVI CONN

Addr: 0b1010000

U38

DVI CODEC

CHRONTEL

Addr: 0b1110110

IIC_SCL_SFP

IIC_SDA_DVI

IIC_SCL_DVI

FMC_LPC_IIC_SDA_LS

FMC_LPC_IIC_SCL_LS

LEVEL LEVEL

SHIFTER SHIFTER

FMC_LPC_IIC_SCL

FMC_LPC_IIC_SDA

IIC_CLK_DVI_F

IIC_SDA_DVI_F

LEVEL

SHIFTER

LEVEL

SHIFTER

IIC_SCL_MAIN

IIC_SDA_MAIN

SFP_MOD_DEF2

SFP_MOD_DEF1

U6

ST MICRO

Addr: 0b1010100 through

0b1010111

J64

FMC HPC

COLUMN C

2 Kb EEPROM on

any FMC LPC

Mezzanine Card

Addr: 0b1010000

J1

DDR3 SODIMM

SOCKET

Addr: 0b1010011 2 Kb EEPROM Addr: 0b0011011 Temperature Sensor

P4

SFP MODULE

CONNECTOR

Addr: 0b1010000

UG534_14_092109

Figure 1-14: IIC Bus Topology

ML605 Hardware User Guide | www.xilinx.com | 43 |

UG534 (v1.2.1) January 21, 2010 |

|

|