Chapter 1: ML605 Evaluation Board

Table

U1 FPGA Pin | Schematic Net Name | Pushbutton | |

Switch Pin | |||

|

| ||

|

|

| |

A19 | GPIO_SW_N | SW5.2 | |

|

|

| |

A18 | GPIO_SW_S | SW6.2 | |

|

|

| |

G17 | GPIO_SW_E | SW7.2 | |

|

|

| |

H17 | GPIO_SW_W | SW8.2 | |

|

|

| |

G26 | GPIO_SW_C | SW9.2 | |

|

|

| |

H10 | CPU_RESET | SW10.2 | |

|

|

|

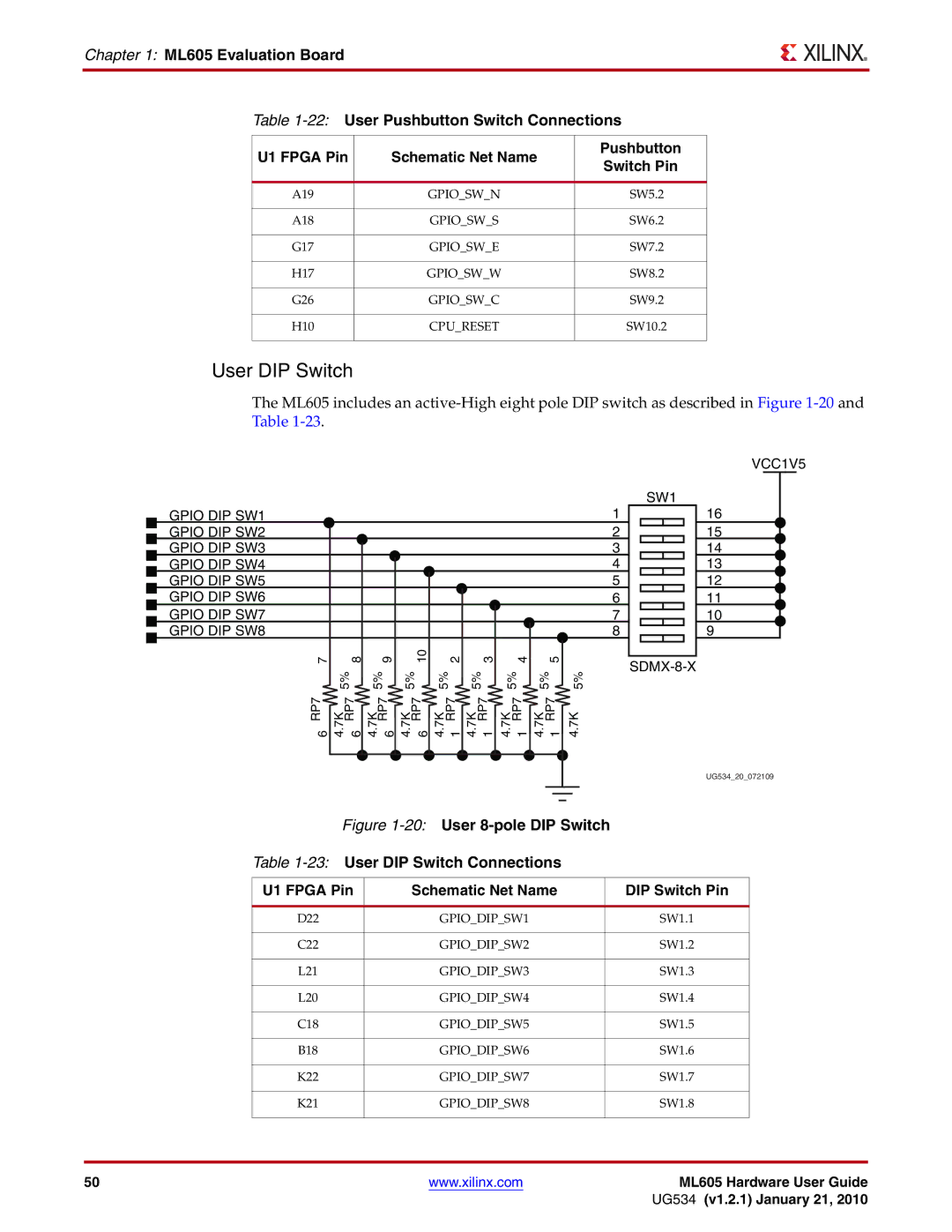

User DIP Switch

The ML605 includes an

VCC1V5

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 |

|

| SW1 | ||||

| GPIO DIP SW1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| GPIO DIP SW2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2 |

|

|

|

|

|

|

|

| GPIO DIP SW3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3 |

|

|

|

|

|

|

|

| GPIO DIP SW4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 4 |

|

|

|

|

|

|

|

| GPIO DIP SW5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 5 |

|

|

|

|

|

|

|

| GPIO DIP SW6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 6 |

|

|

|

|

|

|

|

| GPIO DIP SW7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 7 |

|

|

|

|

|

|

|

| GPIO DIP SW8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 8 |

|

|

|

|

|

|

|

| 7 |

| 8 |

| 9 |

| 10 |

| 2 |

| 3 |

| 4 |

| 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||

|

| 5% | 5% | 5% | 5% | 5% | 5% | 5% | 5% | ||||||||||||||

|

|

|

|

|

|

|

|

| |||||||||||||||

| RP7 | 4.7K | RP7 | 4.7K | RP7 | 4.7K | RP7 | 4.7K | RP7 | 4.7K | RP7 | 4.7K | RP7 | 4.7K | RP7 | 4.7K | |||||||

| 6 | 6 | 6 | 6 | 1 | 1 | 1 | 1 | |||||||||||||||

16

15

14

13

12

11

10

9

|

|

|

| UG534_20_072109 | |

| Figure |

|

| ||

| Table |

|

| ||

|

|

|

|

|

|

| U1 FPGA Pin | Schematic Net Name |

| DIP Switch Pin |

|

|

|

|

|

|

|

| D22 | GPIO_DIP_SW1 |

| SW1.1 |

|

|

|

|

|

|

|

| C22 | GPIO_DIP_SW2 |

| SW1.2 |

|

|

|

|

|

|

|

| L21 | GPIO_DIP_SW3 |

| SW1.3 |

|

|

|

|

|

|

|

| L20 | GPIO_DIP_SW4 |

| SW1.4 |

|

|

|

|

|

|

|

| C18 | GPIO_DIP_SW5 |

| SW1.5 |

|

|

|

|

|

|

|

| B18 | GPIO_DIP_SW6 |

| SW1.6 |

|

|

|

|

|

|

|

| K22 | GPIO_DIP_SW7 |

| SW1.7 |

|

|

|

|

|

|

|

| K21 | GPIO_DIP_SW8 |

| SW1.8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

50 |

| www.xilinx.com | ML605 Hardware User Guide | ||

|

|

|

| UG534 (v1.2.1) January 21, 2010 | |