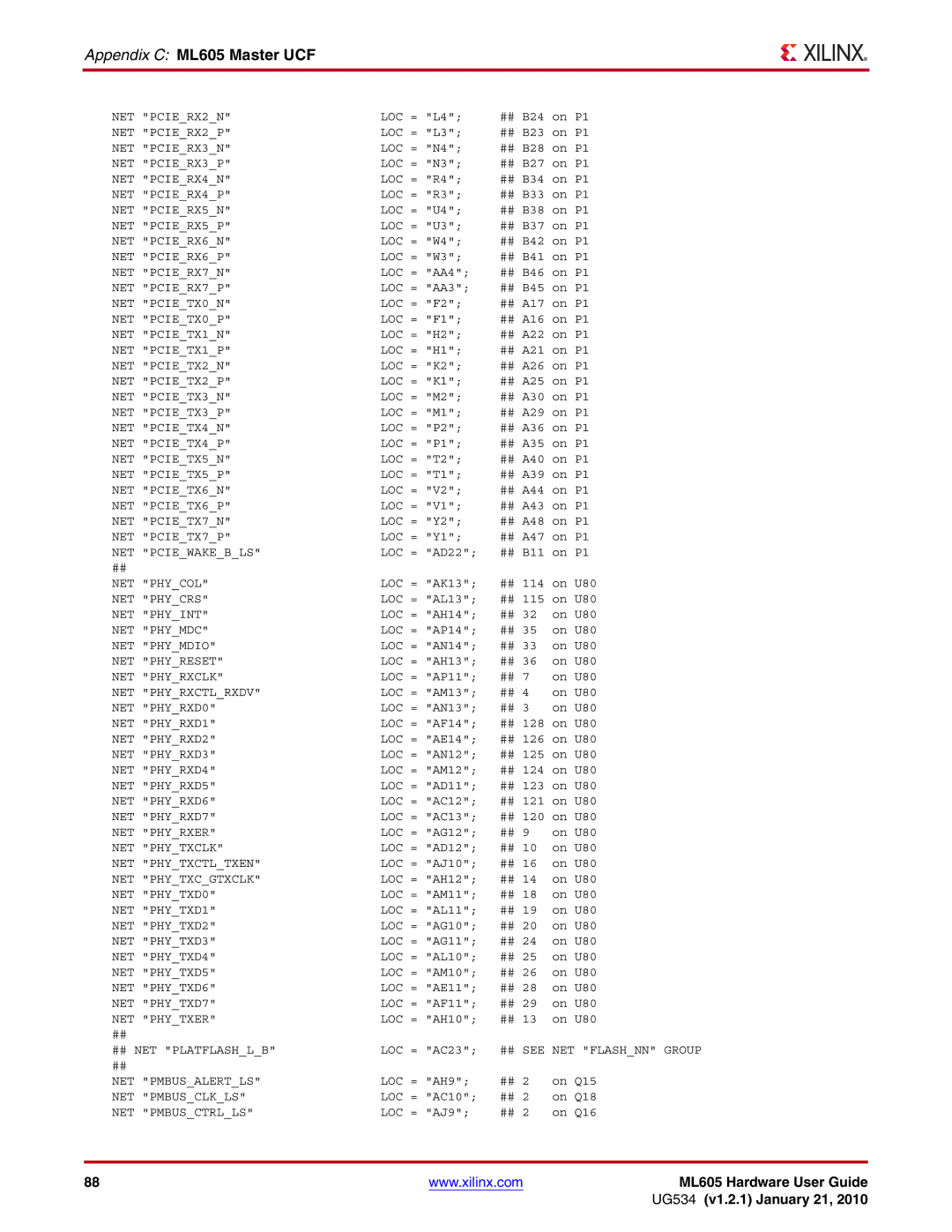

Appendix C: ML605 Master UCF

NET "PCIE_RX2_N" | LOC = "L4"; | ## B24 | on P1 |

NET "PCIE_RX2_P" | LOC = "L3"; | ## B23 | on P1 |

NET "PCIE_RX3_N" | LOC = "N4"; | ## B28 | on P1 |

NET "PCIE_RX3_P" | LOC = "N3"; | ## B27 | on P1 |

NET "PCIE_RX4_N" | LOC = "R4"; | ## B34 | on P1 |

NET "PCIE_RX4_P" | LOC = "R3"; | ## B33 | on P1 |

NET "PCIE_RX5_N" | LOC = "U4"; | ## B38 | on P1 |

NET "PCIE_RX5_P" | LOC = "U3"; | ## B37 | on P1 |

NET "PCIE_RX6_N" | LOC = "W4"; | ## B42 | on P1 |

NET "PCIE_RX6_P" | LOC = "W3"; | ## B41 | on P1 |

NET "PCIE_RX7_N" | LOC = "AA4"; | ## B46 | on P1 |

NET "PCIE_RX7_P" | LOC = "AA3"; | ## B45 | on P1 |

NET "PCIE_TX0_N" | LOC = "F2"; | ## A17 | on P1 |

NET "PCIE_TX0_P" | LOC = "F1"; | ## A16 | on P1 |

NET "PCIE_TX1_N" | LOC = "H2"; | ## A22 | on P1 |

NET "PCIE_TX1_P" | LOC = "H1"; | ## A21 | on P1 |

NET "PCIE_TX2_N" | LOC = "K2"; | ## A26 | on P1 |

NET "PCIE_TX2_P" | LOC = "K1"; | ## A25 | on P1 |

NET "PCIE_TX3_N" | LOC = "M2"; | ## A30 | on P1 |

NET "PCIE_TX3_P" | LOC = "M1"; | ## A29 | on P1 |

NET "PCIE_TX4_N" | LOC = "P2"; | ## A36 | on P1 |

NET "PCIE_TX4_P" | LOC = "P1"; | ## A35 | on P1 |

NET "PCIE_TX5_N" | LOC = "T2"; | ## A40 | on P1 |

NET "PCIE_TX5_P" | LOC = "T1"; | ## A39 | on P1 |

NET "PCIE_TX6_N" | LOC = "V2"; | ## A44 | on P1 |

NET "PCIE_TX6_P" | LOC = "V1"; | ## A43 | on P1 |

NET "PCIE_TX7_N" | LOC = "Y2"; | ## A48 | on P1 |

NET "PCIE_TX7_P" | LOC = "Y1"; | ## A47 | on P1 |

NET "PCIE_WAKE_B_LS" | LOC = "AD22"; | ## B11 | on P1 |

## |

|

|

|

NET "PHY_COL" | LOC = "AK13"; | ## 114 | on U80 |

NET "PHY_CRS" | LOC = "AL13"; | ## 115 | on U80 |

NET "PHY_INT" | LOC = "AH14"; | ## 32 | on U80 |

NET "PHY_MDC" | LOC = "AP14"; | ## 35 | on U80 |

NET "PHY_MDIO" | LOC = "AN14"; | ## 33 | on U80 |

NET "PHY_RESET" | LOC = "AH13"; | ## 36 | on U80 |

NET "PHY_RXCLK" | LOC = "AP11"; | ## 7 | on U80 |

NET "PHY_RXCTL_RXDV" | LOC = "AM13"; | ## 4 | on U80 |

NET "PHY_RXD0" | LOC = "AN13"; | ## 3 | on U80 |

NET "PHY_RXD1" | LOC = "AF14"; | ## 128 | on U80 |

NET "PHY_RXD2" | LOC = "AE14"; | ## 126 | on U80 |

NET "PHY_RXD3" | LOC = "AN12"; | ## 125 | on U80 |

NET "PHY_RXD4" | LOC = "AM12"; | ## 124 | on U80 |

NET "PHY_RXD5" | LOC = "AD11"; | ## 123 | on U80 |

NET "PHY_RXD6" | LOC = "AC12"; | ## 121 | on U80 |

NET "PHY_RXD7" | LOC = "AC13"; | ## 120 | on U80 |

NET "PHY_RXER" | LOC = "AG12"; | ## 9 | on U80 |

NET "PHY_TXCLK" | LOC = "AD12"; | ## 10 | on U80 |

NET "PHY_TXCTL_TXEN" | LOC = "AJ10"; | ## 16 | on U80 |

NET "PHY_TXC_GTXCLK" | LOC = "AH12"; | ## 14 | on U80 |

NET "PHY_TXD0" | LOC = "AM11"; | ## 18 | on U80 |

NET "PHY_TXD1" | LOC = "AL11"; | ## 19 | on U80 |

NET "PHY_TXD2" | LOC = "AG10"; | ## 20 | on U80 |

NET "PHY_TXD3" | LOC = "AG11"; | ## 24 | on U80 |

NET "PHY_TXD4" | LOC = "AL10"; | ## 25 | on U80 |

NET "PHY_TXD5" | LOC = "AM10"; | ## 26 | on U80 |

NET "PHY_TXD6" | LOC = "AE11"; | ## 28 | on U80 |

NET "PHY_TXD7" | LOC = "AF11"; | ## 29 | on U80 |

NET "PHY_TXER" | LOC = "AH10"; | ## 13 | on U80 |

## |

|

|

|

## NET "PLATFLASH_L_B" | LOC = "AC23"; | ## SEE | NET "FLASH_NN" GROUP |

## |

|

|

|

NET "PMBUS_ALERT_LS" | LOC = "AH9"; | ## 2 | on Q15 |

NET "PMBUS_CLK_LS" | LOC = "AC10"; | ## 2 | on Q18 |

NET "PMBUS_CTRL_LS" | LOC = "AJ9"; | ## 2 | on Q16 |

88 | www.xilinx.com | ML605 Hardware User Guide |

|

| UG534 (v1.2.1) January 21, 2010 |