Chapter 1: ML605 Evaluation Board

6. USB JTAG

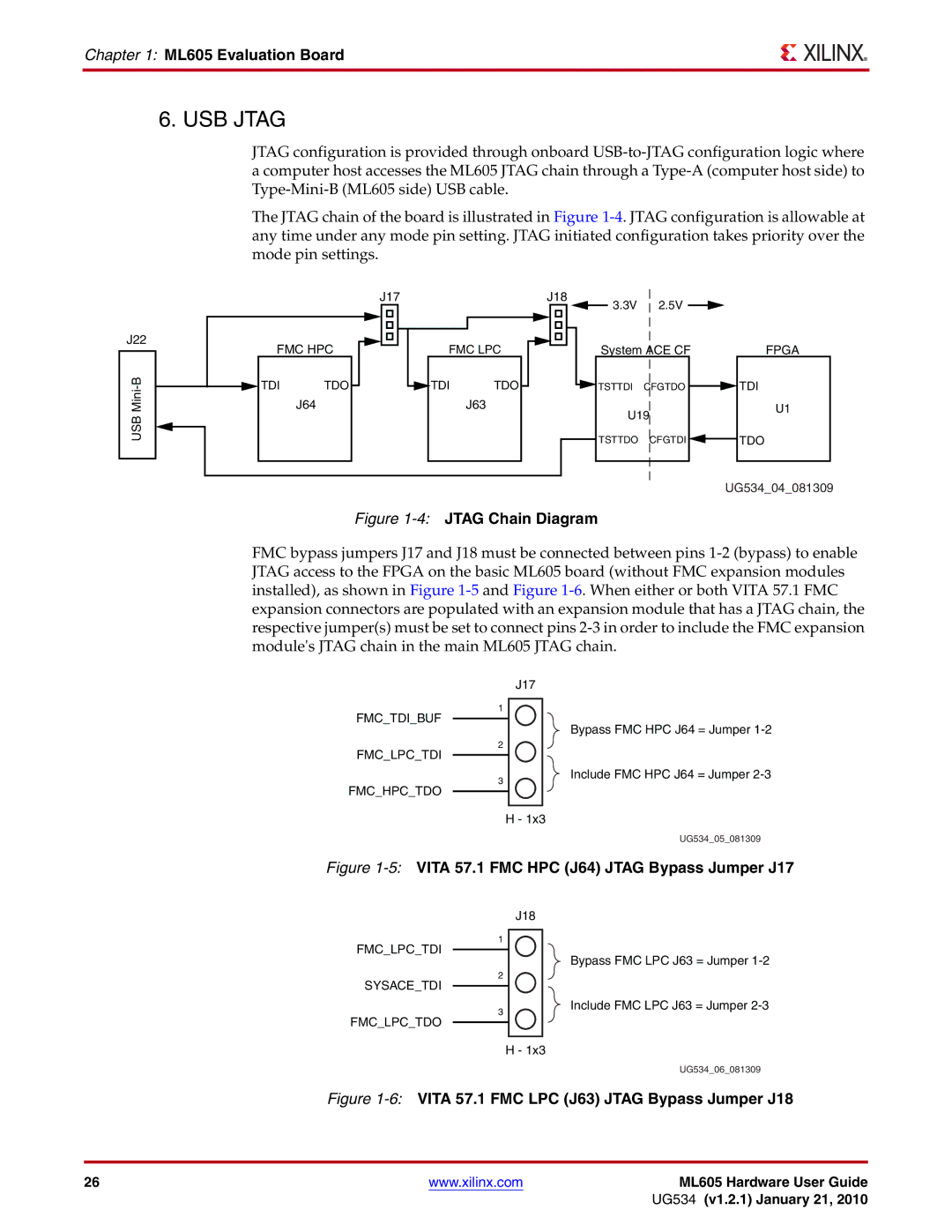

JTAG configuration is provided through onboard

The JTAG chain of the board is illustrated in Figure

J22

USB

FMC HPC

![]() TDI TDO

TDI TDO

J64

J17

FMC LPC

![]() TDI TDO

TDI TDO

J63

J18 |

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

| 3.3V | 2.5V |

|

|

| |||

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

| System ACE CF | FPGA | |||||||

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

| TSTTDI | CFGTDO |

|

|

|

| TDI | ||

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

| U19 |

|

|

|

| U1 | ||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

| TSTTDO | CFGTDI |

|

|

|

| TDO | ||

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UG534_04_081309

Figure 1-4: JTAG Chain Diagram

FMC bypass jumpers J17 and J18 must be connected between pins

J17

1

FMC_TDI_BUF

2

FMC_LPC_TDI

3

FMC_HPC_TDO

Bypass FMC HPC J64 = Jumper

Include FMC HPC J64 = Jumper

H - 1x3

UG534_05_081309

Figure 1-5: VITA 57.1 FMC HPC (J64) JTAG Bypass Jumper J17

J18

1

FMC_LPC_TDI

2

SYSACE_TDI

3

FMC_LPC_TDO

Bypass FMC LPC J63 = Jumper

Include FMC LPC J63 = Jumper

H - 1x3

UG534_06_081309

Figure 1-6: VITA 57.1 FMC LPC (J63) JTAG Bypass Jumper J18

26 | www.xilinx.com | ML605 Hardware User Guide |

|

| UG534 (v1.2.1) January 21, 2010 |