Chapter 1: ML605 Evaluation Board

GTX SMA Clock

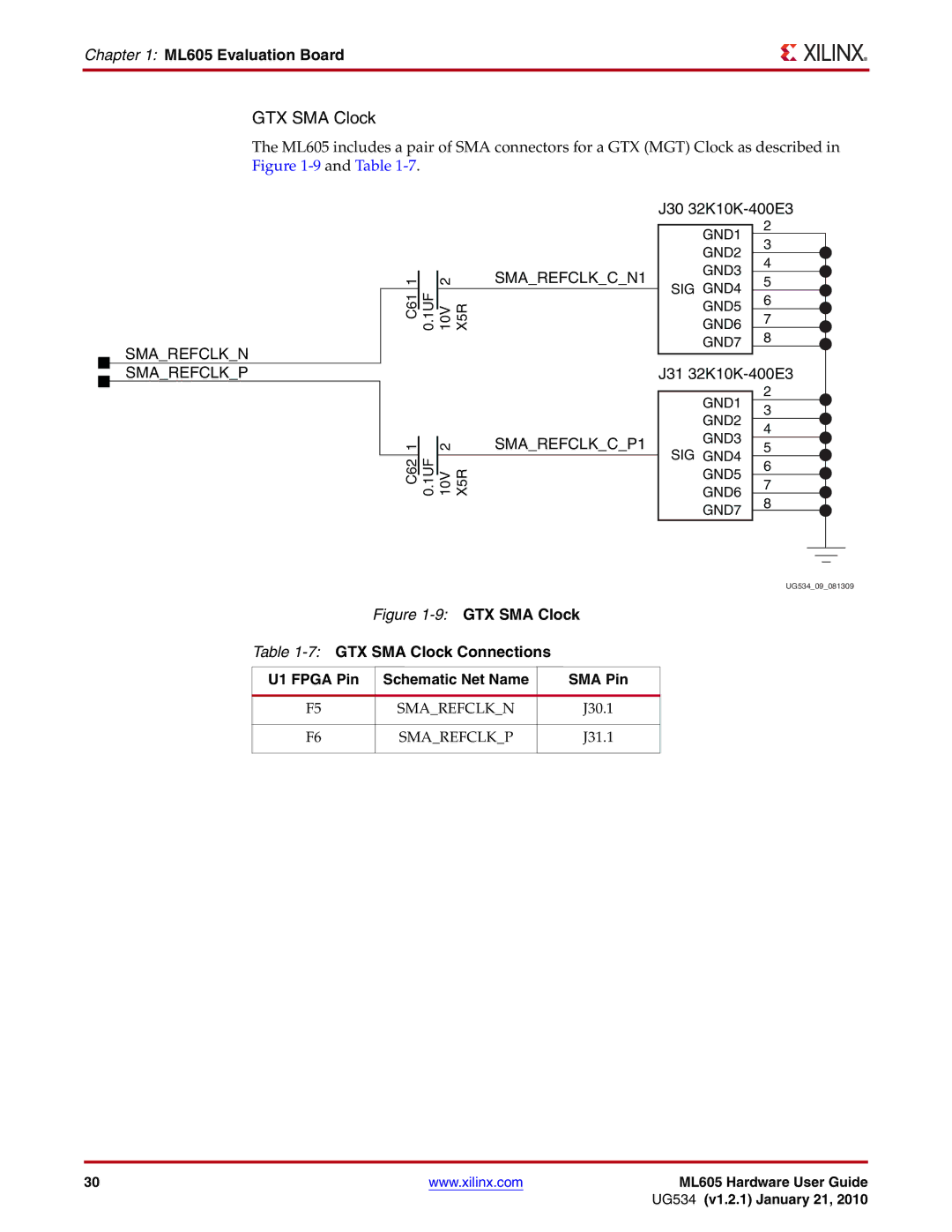

The ML605 includes a pair of SMA connectors for a GTX (MGT) Clock as described in Figure

J30

GND1

GND2 GND3

2

3

4

SMA_REFCLK_N

C61 1

0.1UF

2 |

|

10V | X5R |

SMA_REFCLK_C_N1

SIG GND4 5 GND5 6 GND6 7 GND7 8

SMA_REFCLK_P

C62 1

0.1UF

2 |

|

10V | X5R |

SMA_REFCLK_C_P1

J31

|

| 2 |

|

|

|

|

| GND1 |

|

| |||

| 3 |

|

|

|

| |

| GND2 |

|

|

|

| |

| 4 |

|

|

|

| |

| GND3 |

|

|

|

| |

SIG | 5 |

|

|

|

| |

GND4 |

|

|

|

| ||

6 |

|

|

|

| ||

| GND5 |

|

|

|

| |

| 7 |

|

|

|

| |

| GND6 |

|

|

|

| |

| 8 |

|

|

|

| |

| GND7 |

|

|

|

| |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UG534_09_081309

Figure 1-9: GTX SMA Clock

Table 1-7: GTX SMA Clock Connections

U1 FPGA Pin | Schematic Net Name | SMA Pin |

|

|

|

F5 | SMA_REFCLK_N | J30.1 |

|

|

|

F6 | SMA_REFCLK_P | J31.1 |

|

|

|

30 | www.xilinx.com | ML605 Hardware User Guide |

|

| UG534 (v1.2.1) January 21, 2010 |