|

|

|

|

|

|

| Detailed Description |

|

|

|

|

|

|

|

|

|

|

| Table | ||||

|

|

|

|

|

|

|

|

|

|

| Pin | Connection on | Bit[2] | Bit[1] | Bit[0] |

|

|

| Board | Definition and Value | Definition and Value | Definition and Value | |

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

| CFG5 | VCC 2.5V | DIS_FC = 1 | DIS_SLEEP = 1 | HWCFG_MD[3] = 1 |

|

|

| CFG6 | PHY_LED_RX | SEL_BDT = 0 | INT_POL = 1 | 75/50 OHM = 0 |

|

|

|

|

|

|

|

|

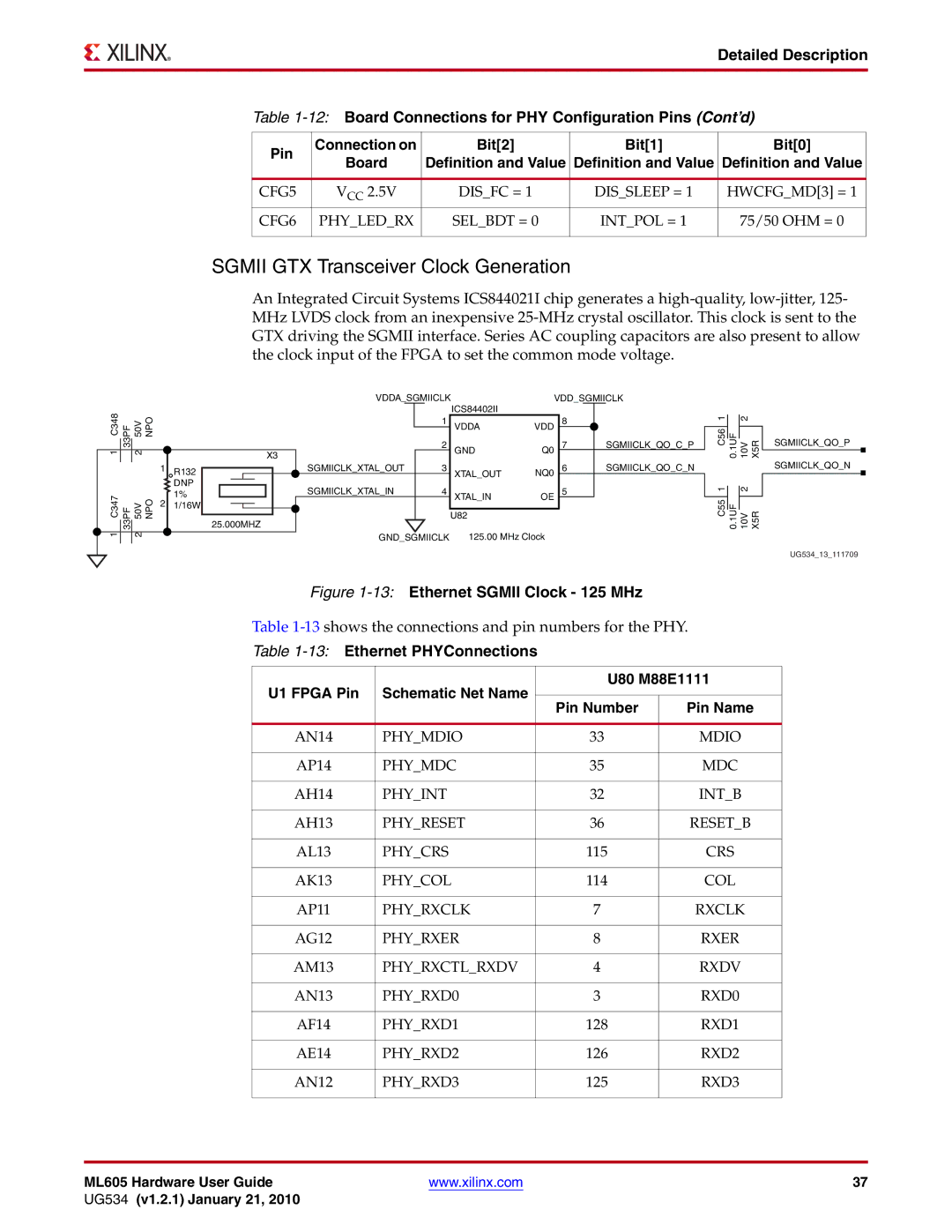

SGMII GTX Transceiver Clock Generation

An Integrated Circuit Systems ICS844021I chip generates a

C348 |

| 33PF |

| 50V | NPO |

1 |

|

| 2 |

| |

|

|

|

| ||

C347 |

| 33PF |

| 50V | NPO |

|

| ||||

1 |

|

| 2 |

| |

|

|

|

| ||

|

|

|

|

|

|

1R132 DNP 1%

21/16W

|

|

|

|

|

| VDDA_SGMIICLK |

| VDD_SGMIICLK | ||||||||

|

|

|

|

|

|

|

|

|

| ICS84402II |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 | VDDA | VDD | 8 |

|

| SGMIICLK_QO_C_P |

| |

|

|

|

| X3 |

|

| 2 | GND | Q0 | 7 |

|

|

| |||

|

|

|

|

|

| SGMIICLK_XTAL_OUT | 3 | XTAL_OUT | NQ0 | 6 |

|

| SGMIICLK_QO_C_N | |||

|

|

|

|

|

| SGMIICLK_XTAL_IN | 4 | XTAL_IN | OE | 5 |

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

| U82 |

|

|

|

|

|

|

25.000MHZ |

|

|

|

|

|

|

|

|

|

| ||||||

GND_SGMIICLK | 125.00 MHz Clock |

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

| ||||||

C55 1 C56 1

0.1UF 0.1UF

| 2 |

|

|

|

|

|

|

| 10V | X5R |

|

|

| ||

|

| ||

|

|

| |

| 2 |

|

|

|

|

| |

|

|

|

|

| 10V | X5R | |

| |||

SGMIICLK_QO_P

SGMIICLK_QO_N

UG534_13_111709

Figure 1-13: Ethernet SGMII Clock - 125 MHz

Table

Table 1-13: Ethernet PHYConnections

U1 FPGA Pin | Schematic Net Name | U80 M88E1111 | ||

|

| |||

Pin Number | Pin Name | |||

|

| |||

|

|

|

| |

AN14 | PHY_MDIO | 33 | MDIO | |

|

|

|

| |

AP14 | PHY_MDC | 35 | MDC | |

|

|

|

| |

AH14 | PHY_INT | 32 | INT_B | |

|

|

|

| |

AH13 | PHY_RESET | 36 | RESET_B | |

|

|

|

| |

AL13 | PHY_CRS | 115 | CRS | |

|

|

|

| |

AK13 | PHY_COL | 114 | COL | |

|

|

|

| |

AP11 | PHY_RXCLK | 7 | RXCLK | |

|

|

|

| |

AG12 | PHY_RXER | 8 | RXER | |

|

|

|

| |

AM13 | PHY_RXCTL_RXDV | 4 | RXDV | |

|

|

|

| |

AN13 | PHY_RXD0 | 3 | RXD0 | |

|

|

|

| |

AF14 | PHY_RXD1 | 128 | RXD1 | |

|

|

|

| |

AE14 | PHY_RXD2 | 126 | RXD2 | |

|

|

|

| |

AN12 | PHY_RXD3 | 125 | RXD3 | |

|

|

|

| |

ML605 Hardware User Guide | www.xilinx.com | 37 |

UG534 (v1.2.1) January 21, 2010 |

|

|