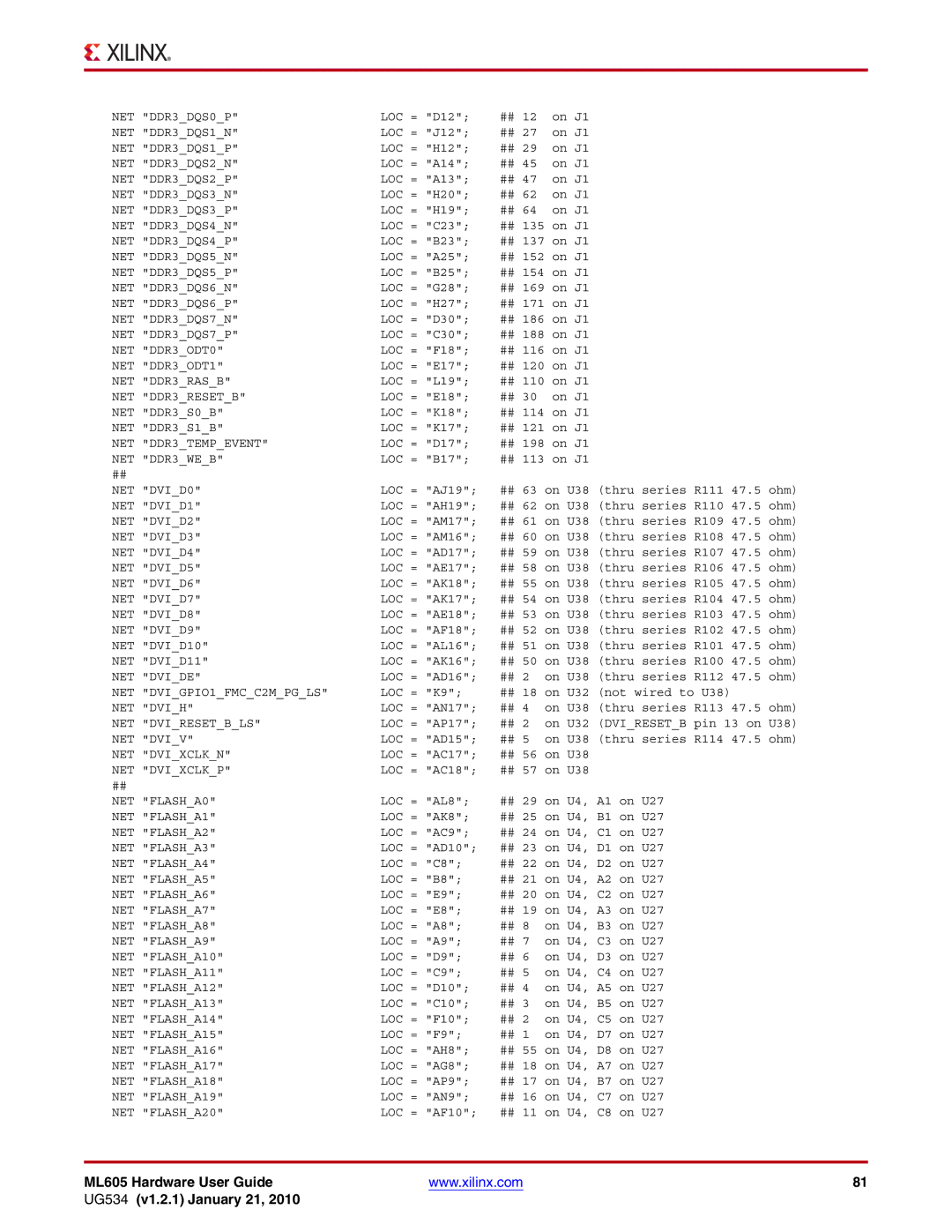

NET "DDR3_DQS0_P" | LOC = "D12"; |

NET "DDR3_DQS1_N" | LOC = "J12"; |

NET "DDR3_DQS1_P" | LOC = "H12"; |

NET "DDR3_DQS2_N" | LOC = "A14"; |

NET "DDR3_DQS2_P" | LOC = "A13"; |

NET "DDR3_DQS3_N" | LOC = "H20"; |

NET "DDR3_DQS3_P" | LOC = "H19"; |

NET "DDR3_DQS4_N" | LOC = "C23"; |

NET "DDR3_DQS4_P" | LOC = "B23"; |

NET "DDR3_DQS5_N" | LOC = "A25"; |

NET "DDR3_DQS5_P" | LOC = "B25"; |

NET "DDR3_DQS6_N" | LOC = "G28"; |

NET "DDR3_DQS6_P" | LOC = "H27"; |

NET "DDR3_DQS7_N" | LOC = "D30"; |

NET "DDR3_DQS7_P" | LOC = "C30"; |

NET "DDR3_ODT0" | LOC = "F18"; |

NET "DDR3_ODT1" | LOC = "E17"; |

NET "DDR3_RAS_B" | LOC = "L19"; |

NET "DDR3_RESET_B" | LOC = "E18"; |

NET "DDR3_S0_B" | LOC = "K18"; |

NET "DDR3_S1_B" | LOC = "K17"; |

NET "DDR3_TEMP_EVENT" | LOC = "D17"; |

NET "DDR3_WE_B" | LOC = "B17"; |

## |

|

NET "DVI_D0" | LOC = "AJ19"; |

NET "DVI_D1" | LOC = "AH19"; |

NET "DVI_D2" | LOC = "AM17"; |

NET "DVI_D3" | LOC = "AM16"; |

NET "DVI_D4" | LOC = "AD17"; |

NET "DVI_D5" | LOC = "AE17"; |

NET "DVI_D6" | LOC = "AK18"; |

NET "DVI_D7" | LOC = "AK17"; |

NET "DVI_D8" | LOC = "AE18"; |

NET "DVI_D9" | LOC = "AF18"; |

NET "DVI_D10" | LOC = "AL16"; |

NET "DVI_D11" | LOC = "AK16"; |

NET "DVI_DE" | LOC = "AD16"; |

NET "DVI_GPIO1_FMC_C2M_PG_LS" | LOC = "K9"; |

NET "DVI_H" | LOC = "AN17"; |

NET "DVI_RESET_B_LS" | LOC = "AP17"; |

NET "DVI_V" | LOC = "AD15"; |

NET "DVI_XCLK_N" | LOC = "AC17"; |

NET "DVI_XCLK_P" | LOC = "AC18"; |

## |

|

NET "FLASH_A0" | LOC = "AL8"; |

NET "FLASH_A1" | LOC = "AK8"; |

NET "FLASH_A2" | LOC = "AC9"; |

NET "FLASH_A3" | LOC = "AD10"; |

NET "FLASH_A4" | LOC = "C8"; |

NET "FLASH_A5" | LOC = "B8"; |

NET "FLASH_A6" | LOC = "E9"; |

NET "FLASH_A7" | LOC = "E8"; |

NET "FLASH_A8" | LOC = "A8"; |

NET "FLASH_A9" | LOC = "A9"; |

NET "FLASH_A10" | LOC = "D9"; |

NET "FLASH_A11" | LOC = "C9"; |

NET "FLASH_A12" | LOC = "D10"; |

NET "FLASH_A13" | LOC = "C10"; |

NET "FLASH_A14" | LOC = "F10"; |

NET "FLASH_A15" | LOC = "F9"; |

NET "FLASH_A16" | LOC = "AH8"; |

NET "FLASH_A17" | LOC = "AG8"; |

NET "FLASH_A18" | LOC = "AP9"; |

NET "FLASH_A19" | LOC = "AN9"; |

NET "FLASH_A20" | LOC = "AF10"; |

##12 on J1

##27 on J1

##29 on J1

##45 on J1

##47 on J1

##62 on J1

##64 on J1

##135 on J1

##137 on J1

##152 on J1

##154 on J1

##169 on J1

##171 on J1

##186 on J1

##188 on J1

##116 on J1

##120 on J1

##110 on J1

##30 on J1

##114 on J1

##121 on J1

##198 on J1

##113 on J1

##63 on U38 (thru series R111 47.5 ohm)

##62 on U38 (thru series R110 47.5 ohm)

##61 on U38 (thru series R109 47.5 ohm)

##60 on U38 (thru series R108 47.5 ohm)

##59 on U38 (thru series R107 47.5 ohm)

##58 on U38 (thru series R106 47.5 ohm)

##55 on U38 (thru series R105 47.5 ohm)

##54 on U38 (thru series R104 47.5 ohm)

##53 on U38 (thru series R103 47.5 ohm)

##52 on U38 (thru series R102 47.5 ohm)

##51 on U38 (thru series R101 47.5 ohm)

##50 on U38 (thru series R100 47.5 ohm)

##2 on U38 (thru series R112 47.5 ohm)

##18 on U32 (not wired to U38)

##4 on U38 (thru series R113 47.5 ohm)

##2 on U32 (DVI_RESET_B pin 13 on U38)

##5 on U38 (thru series R114 47.5 ohm)

##56 on U38

##57 on U38

##29 on U4, A1 on U27

##25 on U4, B1 on U27

##24 on U4, C1 on U27

##23 on U4, D1 on U27

##22 on U4, D2 on U27

##21 on U4, A2 on U27

##20 on U4, C2 on U27

##19 on U4, A3 on U27

##8 on U4, B3 on U27

##7 on U4, C3 on U27

##6 on U4, D3 on U27

##5 on U4, C4 on U27

##4 on U4, A5 on U27

##3 on U4, B5 on U27

##2 on U4, C5 on U27

##1 on U4, D7 on U27

##55 on U4, D8 on U27

##18 on U4, A7 on U27

##17 on U4, B7 on U27

##16 on U4, C7 on U27

##11 on U4, C8 on U27

ML605 Hardware User Guide | www.xilinx.com | 81 |

UG534 (v1.2.1) January 21, 2010 |

|

|