PLB PCI Full Bridge (v1.00a)

PLB PCI Bus Interface I/O Signals

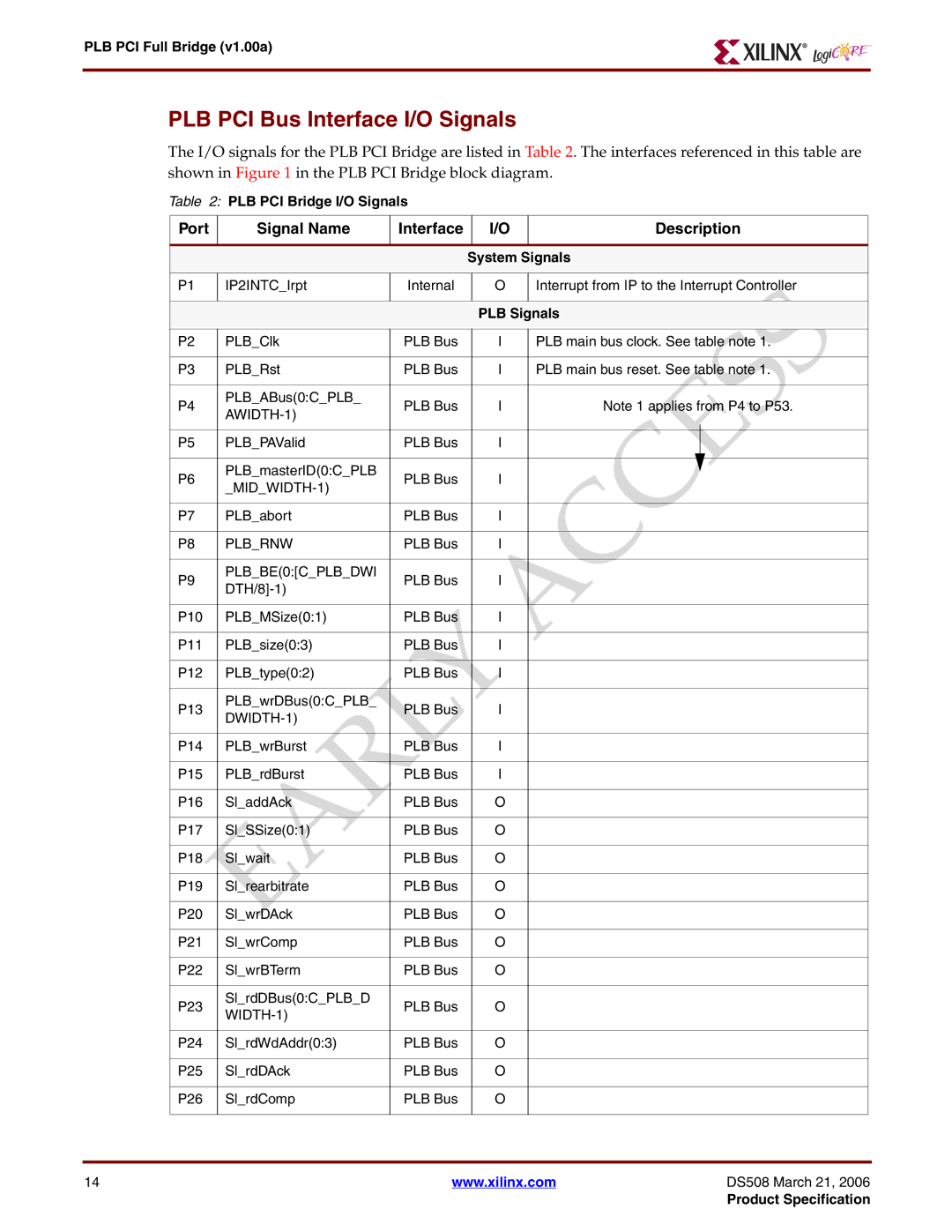

The I/O signals for the PLB PCI Bridge are listed in Table 2. The interfaces referenced in this table are shown in Figure 1 in the PLB PCI Bridge block diagram.

Table 2: PLB PCI Bridge I/O Signals

Port

Signal Name

Interface

I/O

Description

System Signals

P1

IP2INTC_Irpt

Internal

O

Interrupt from IP to the Interrupt Controller

PLB Signals

P2 | PLB_Clk | PLB Bus | I | PLB main bus clock. See table note 1. | ||

|

|

|

|

|

| |

P3 | PLB_Rst | PLB Bus | I | PLB main bus reset. See table note 1. | ||

|

|

|

|

|

| |

P4 | PLB_ABus(0:C_PLB_ | PLB Bus | I | Note 1 applies from P4 to P53. | ||

|

|

|

|

| ||

|

|

|

|

|

| |

|

|

|

|

|

| |

P5 | PLB_PAValid | PLB Bus | I |

|

| |

|

|

|

|

|

| |

P6 | PLB_masterID(0:C_PLB | PLB Bus | I |

|

| |

|

| |||||

|

|

|

|

| ||

|

|

|

|

|

| |

P7 | PLB_abort | PLB Bus | I |

|

| |

|

|

|

|

|

| |

P8 | PLB_RNW | PLB Bus | I |

|

| |

|

|

|

|

|

| |

P9 | PLB_BE(0:[C_PLB_DWI | PLB Bus | I |

|

| |

|

| |||||

|

|

|

|

| ||

|

|

|

|

|

| |

P10 | PLB_MSize(0:1) | PLB Bus | I |

|

| |

|

|

|

|

|

| |

P11 | PLB size(0:3) | PLB Bus | I |

|

| |

|

|

|

|

|

| |

P12 | PLB type(0:2) | PLB Bus | I |

|

| |

|

|

|

|

|

| |

P13 | PLB wrDBus(0:C PLB | PLB Bus | I |

|

| |

|

|

| ||||

|

|

|

|

| ||

|

|

|

|

|

| |

P14 | PLB wrBurst | PLB Bus | I |

|

| |

|

|

|

|

|

| |

P15 | PLB rdBurst | PLB Bus | I |

|

| |

|

|

|

|

|

| |

P16 | Sl addAck | PLB Bus | O |

|

| |

|

|

|

|

|

| |

P17 | Sl SSize(0:1) | PLB Bus | O |

|

| |

|

|

|

|

|

| |

P18 | Sl wait | PLB Bus | O |

|

| |

|

|

|

|

|

| |

P19 | Sl rearbitrate | PLB Bus | O |

|

| |

|

|

|

|

|

| |

P20 | Sl wrDAck | PLB Bus | O |

|

| |

|

|

|

|

|

| |

P21 | Sl wrComp | PLB Bus | O |

|

| |

|

|

|

|

|

| |

P22 | Sl_wrBTerm | PLB Bus | O |

|

| |

|

|

|

|

|

| |

P23 | Sl_rdDBus(0:C_PLB_D | PLB Bus | O |

|

| |

|

| |||||

|

|

|

|

| ||

|

|

|

|

|

| |

P24 | Sl_rdWdAddr(0:3) | PLB Bus | O |

|

| |

|

|

|

|

|

| |

P25 | Sl_rdDAck | PLB Bus | O |

|

| |

|

|

|

|

|

| |

P26 | Sl_rdComp | PLB Bus | O |

|

| |

|

|

|

|

|

| |

14 | www.xilinx.com | DS508 March 21, 2006 |

|

| Product Specification |