PLB PCI Full Bridge (v1.00a)

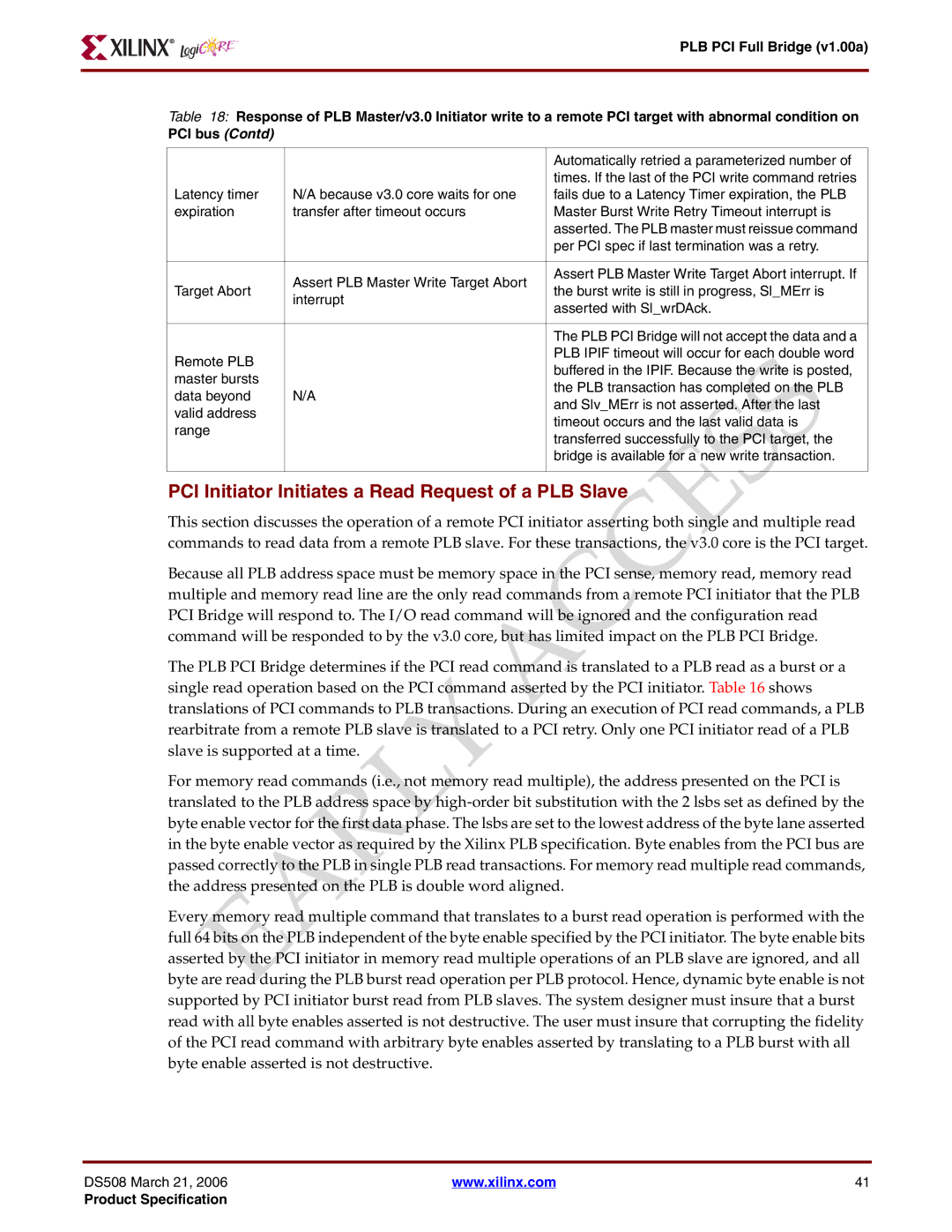

Table 18: Response of PLB Master/v3.0 Initiator write to a remote PCI target with abnormal condition on

PCI bus (Contd)

|

| Automatically retried a parameterized number of | |

|

| times. If the last of the PCI write command retries | |

Latency timer | N/A because v3.0 core waits for one | fails due to a Latency Timer expiration, the PLB | |

expiration | transfer after timeout occurs | Master Burst Write Retry Timeout interrupt is | |

|

| asserted. The PLB master must reissue command | |

|

| per PCI spec if last termination was a retry. | |

|

|

| |

| Assert PLB Master Write Target Abort | Assert PLB Master Write Target Abort interrupt. If | |

Target Abort | the burst write is still in progress, Sl_MErr is | ||

interrupt | |||

| asserted with Sl_wrDAck. | ||

|

| ||

|

|

| |

|

| The PLB PCI Bridge will not accept the data and a | |

Remote PLB |

| PLB IPIF timeout will occur for each double word | |

| buffered in the IPIF. Because the write is posted, | ||

master bursts |

| ||

| the PLB transaction has completed on the PLB | ||

data beyond | N/A | ||

and Slv MErr is not asserted. After the last | |||

valid address |

| ||

| timeout occurs and the last valid data is | ||

range |

| ||

| transferred successfully to the PCI target, the | ||

|

| ||

|

| bridge is available for a new write transaction. | |

|

|

|

PCI Initiator Initiates a Read Request of a PLB Slave

This section discusses the operation of a remote PCI initiator asserting both single and multiple read commands to read data from a remote PLB slave. For these transactions, the v3.0 core is the PCI target.

Because all PLB address space must be memory space in the PCI sense, memory read, memory read multiple and memory read line are the only read commands from a remote PCI initiator that the PLB PCI Bridge will respond to. The I/O read command will be ignored and the configuration read command will be responded to by the v3.0 core, but has limited impact on the PLB PCI Bridge.

The PLB PCI Bridge determines if the PCI read command is translated to a PLB read as a burst or a single read operation based on the PCI command asserted by the PCI initiator. Table 16 shows translations of PCI commands to PLB transactions. During an execution of PCI read commands, a PLB rearbitrate from a remote PLB slave is translated to a PCI retry. Only one PCI initiator read of a PLB slave is supported at a time.

For memory read commands (i.e., not memory read multiple), the address presented on the PCI is translated to the PLB address space by

Every memory read multiple command that translates to a burst read operation is performed with the full 64 bits on the PLB independent of the byte enable specified by the PCI initiator. The byte enable bits asserted by the PCI initiator in memory read multiple operations of an PLB slave are ignored, and all byte are read during the PLB burst read operation per PLB protocol. Hence, dynamic byte enable is not supported by PCI initiator burst read from PLB slaves. The system designer must insure that a burst read with all byte enables asserted is not destructive. The user must insure that corrupting the fidelity of the PCI read command with arbitrary byte enables asserted by translating to a PLB burst with all byte enable asserted is not destructive.

DS508 March 21, 2006 | www.xilinx.com | 41 |

Product Specification