PLB PCI Full Bridge (v1.00a)

the

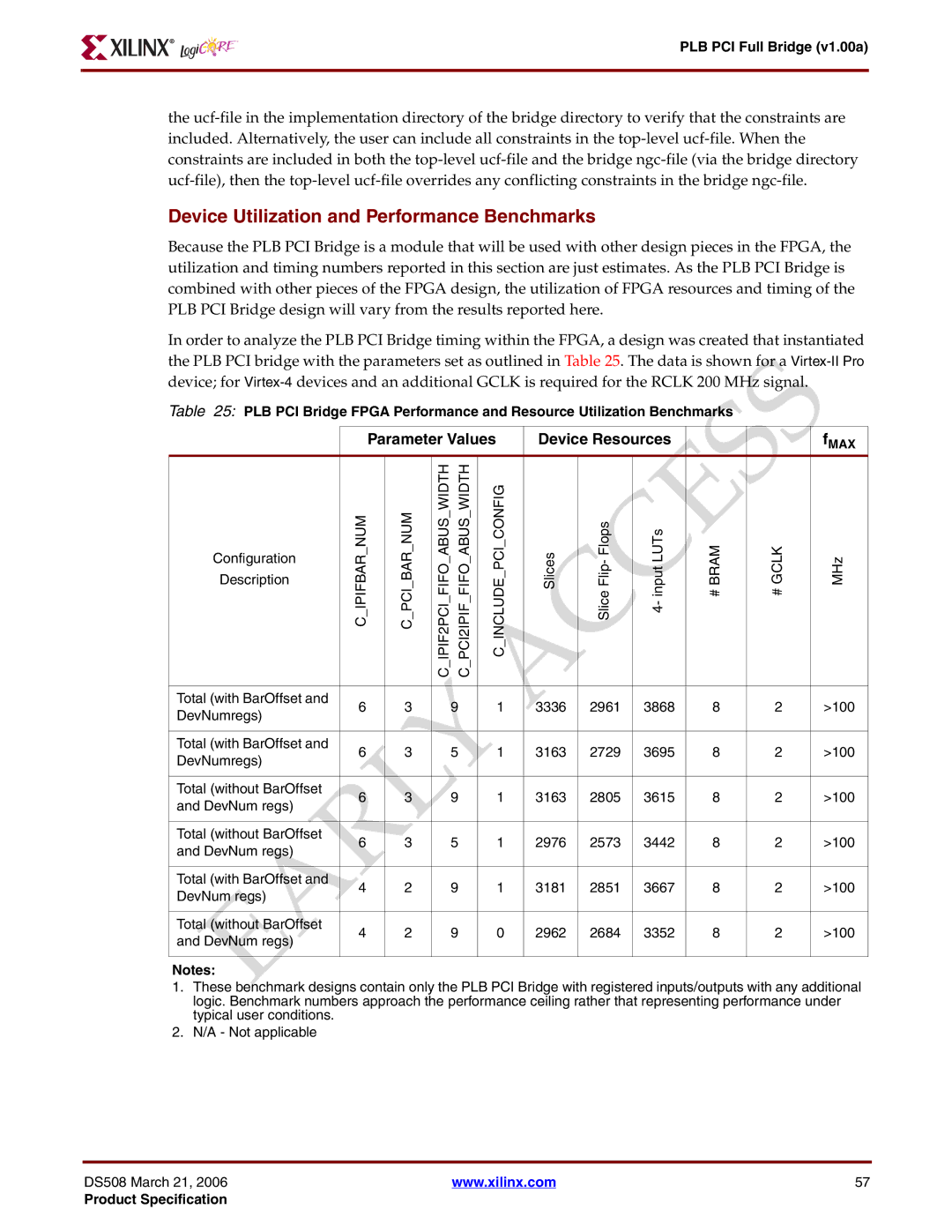

Device Utilization and Performance Benchmarks

Because the PLB PCI Bridge is a module that will be used with other design pieces in the FPGA, the utilization and timing numbers reported in this section are just estimates. As the PLB PCI Bridge is combined with other pieces of the FPGA design, the utilization of FPGA resources and timing of the PLB PCI Bridge design will vary from the results reported here.

In order to analyze the PLB PCI Bridge timing within the FPGA, a design was created that instantiated the PLB PCI bridge with the parameters set as outlined in Table 25. The data is shown for a

Table 25: PLB PCI Bridge FPGA Performance and Resource Utilization Benchmarks |

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

| |

|

| Parameter Values | Device Resources |

|

| fMAX | ||||||

Configuration | _IPIFBARC_NUM |

| __BARPCIC_NUM | ___FIFOIPIF2PCICABUS_WIDTH | ___FIFOPCI2IPIFCABUS_WIDTH | __PCIINCLUDEC _CONFIG | Slices | BRAM# | GCLK# | MHz | ||

|

|

|

|

|

|

|

|

|

|

|

| |

Description |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Total (with BarOffset and | 6 |

| 3 |

| 9 | 1 | 3336 | 2961 | 3868 | 8 | 2 | >100 |

DevNumregs) |

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

Total (with BarOffset and | 6 |

| 3 |

| 5 | 1 | 3163 | 2729 | 3695 | 8 | 2 | >100 |

DevNumregs) |

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

Total (without BarOffset | 6 |

| 3 |

| 9 | 1 | 3163 | 2805 | 3615 | 8 | 2 | >100 |

and DevNum regs) |

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

Total (without BarOffset | 6 |

| 3 |

| 5 | 1 | 2976 | 2573 | 3442 | 8 | 2 | >100 |

and DevNum regs) |

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

Total (with BarOffset and | 4 |

| 2 |

| 9 | 1 | 3181 | 2851 | 3667 | 8 | 2 | >100 |

DevNum regs) |

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

Total (without BarOffset | 4 |

| 2 |

| 9 | 0 | 2962 | 2684 | 3352 | 8 | 2 | >100 |

and DevNum regs) |

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

Notes: |

|

|

|

|

|

|

|

|

|

|

|

|

1.These benchmark designs contain only the PLB PCI Bridge with registered inputs/outputs with any additional logic. Benchmark numbers approach the performance ceiling rather that representing performance under typical user conditions.

2.N/A - Not applicable

DS508 March 21, 2006 | www.xilinx.com | 57 |

Product Specification