|

|

|

|

|

|

|

| PLB PCI Full Bridge (v1.00a) |

|

|

|

|

|

|

|

|

|

|

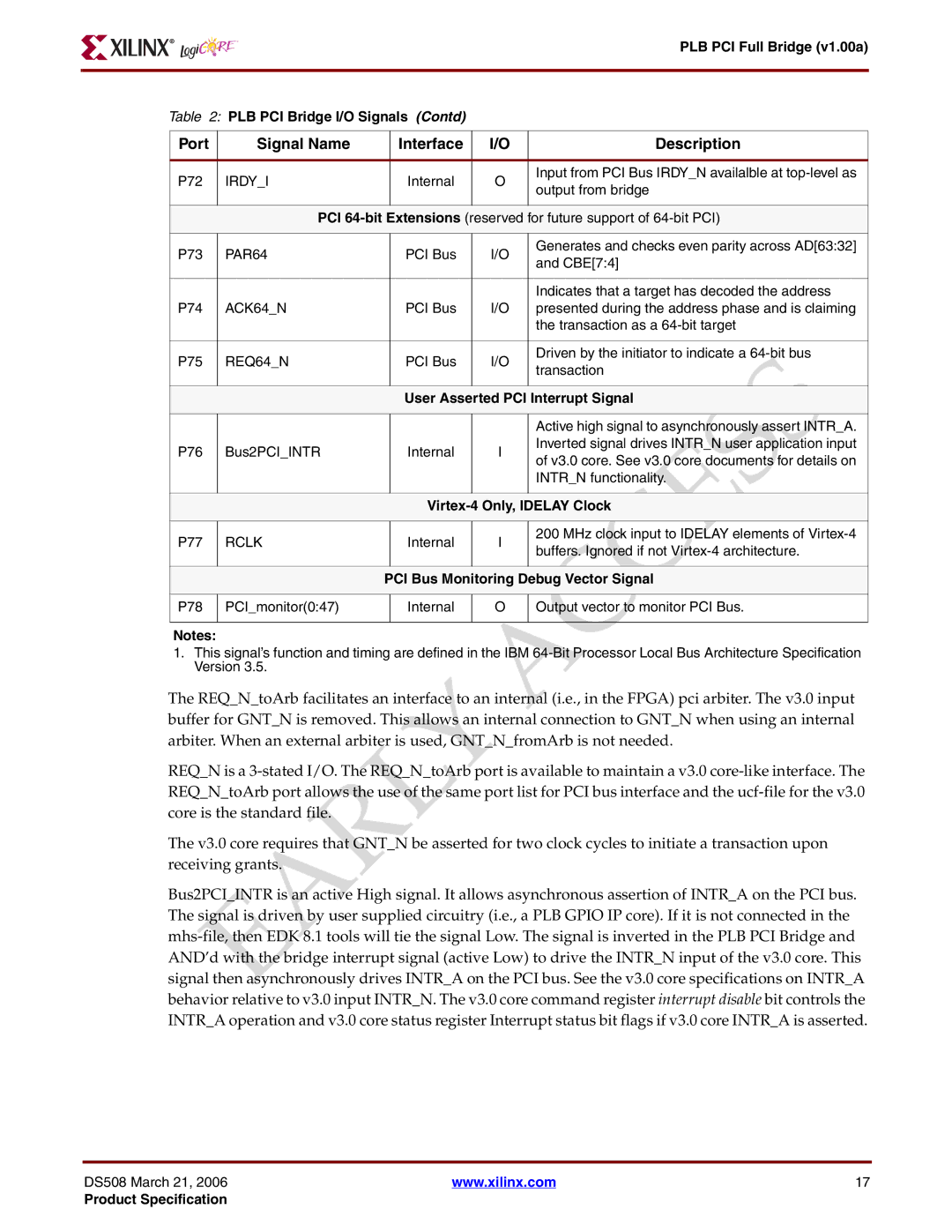

| Table 2: PLB PCI Bridge I/O Signals (Contd) |

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

| Port | Signal Name |

| Interface | I/O | Description |

|

|

|

|

|

|

|

|

|

|

|

| P72 | IRDY_I |

| Internal | O | Input from PCI Bus IRDY_N availalble at |

|

|

|

| output from bridge | ||||

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| |

|

|

|

| PCI | ||||

|

|

|

|

|

|

|

|

|

|

|

| P73 | PAR64 |

| PCI Bus | I/O | Generates and checks even parity across AD[63:32] |

|

|

|

| and CBE[7:4] | ||||

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Indicates that a target has decoded the address |

|

|

| P74 | ACK64_N |

| PCI Bus | I/O | presented during the address phase and is claiming |

|

|

|

|

|

|

|

| the transaction as a |

|

|

|

|

|

|

|

|

|

|

|

| P75 | REQ64_N |

| PCI Bus | I/O | Driven by the initiator to indicate a |

|

|

|

| transaction | ||||

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| User Asserted PCI Interrupt Signal | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Active high signal to asynchronously assert INTR_A. |

|

|

| P76 | Bus2PCI_INTR |

| Internal | I | Inverted signal drives INTR N user application input |

|

|

|

| of v3.0 core. See v3.0 core documents for details on | ||||

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| INTR N functionality. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

| P77 | RCLK |

| Internal | I | 200 MHz clock input to IDELAY elements of |

|

|

|

| buffers. Ignored if not | ||||

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| PCI Bus Monitoring Debug Vector Signal | |||

|

|

|

|

|

|

|

|

|

|

|

| P78 | PCI_monitor(0:47) |

| Internal | O | Output vector to monitor PCI Bus. |

|

|

|

|

|

|

|

|

|

Notes:

1.This signal’s function and timing are defined in the IBM

The REQ_N_toArb facilitates an interface to an internal (i.e., in the FPGA) pci arbiter. The v3.0 input buffer for GNT_N is removed. This allows an internal connection to GNT N when using an internal arbiter. When an external arbiter is used, GNT_N_fromArb is not needed.

REQ_N is a

The v3.0 core requires that GNT N be asserted for two clock cycles to initiate a transaction upon receiving grants.

Bus2PCI_INTR is an active High signal. It allows asynchronous assertion of INTR_A on the PCI bus. The signal is driven by user supplied circuitry (i.e., a PLB GPIO IP core). If it is not connected in the

DS508 March 21, 2006 | www.xilinx.com | 17 |

Product Specification