PLB PCI Full Bridge (v1.00a)

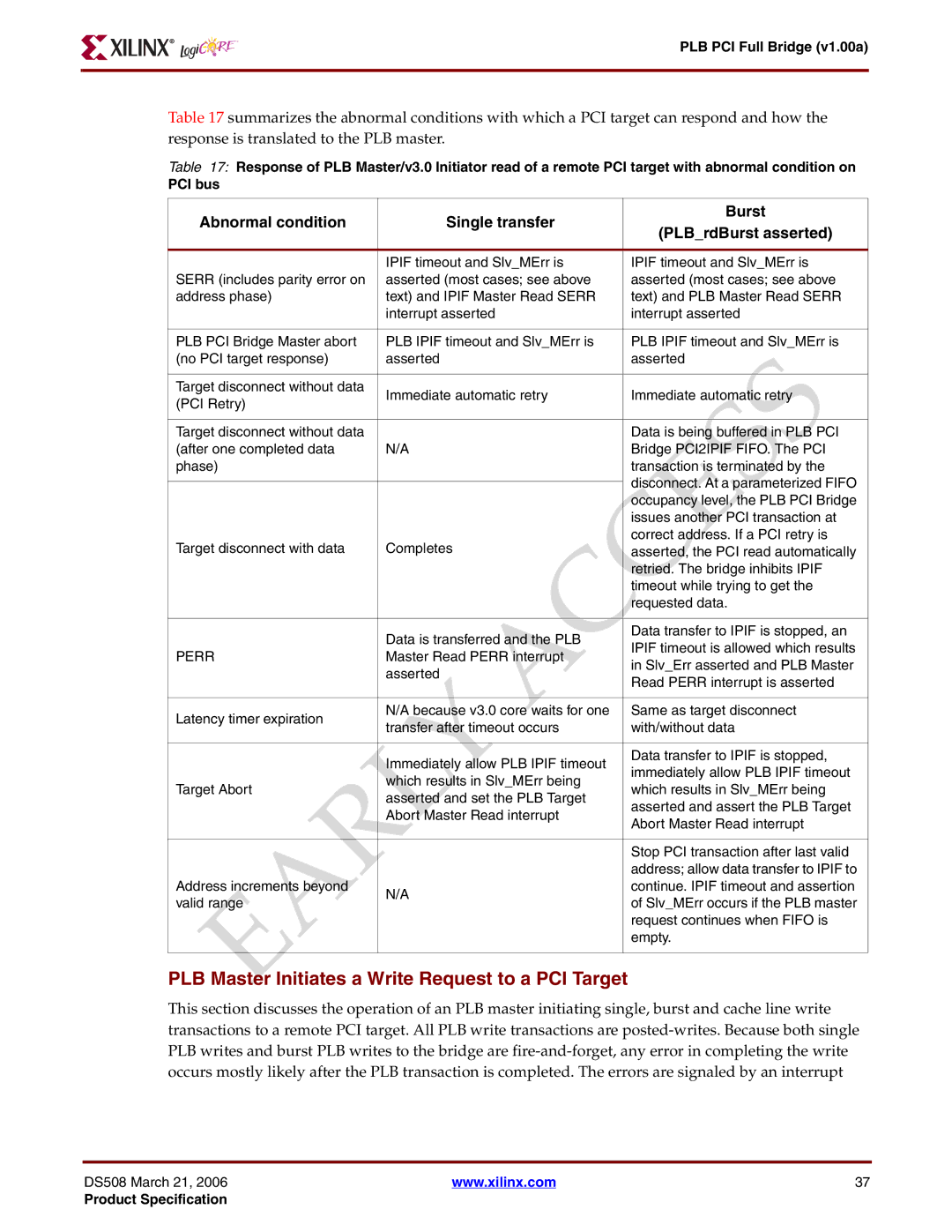

Table 17 summarizes the abnormal conditions with which a PCI target can respond and how the response is translated to the PLB master.

Table 17: Response of PLB Master/v3.0 Initiator read of a remote PCI target with abnormal condition on

PCI bus

Abnormal condition | Single transfer | Burst | |

(PLB_rdBurst asserted) | |||

|

| ||

|

|

| |

| IPIF timeout and Slv_MErr is | IPIF timeout and Slv_MErr is | |

SERR (includes parity error on | asserted (most cases; see above | asserted (most cases; see above | |

address phase) | text) and IPIF Master Read SERR | text) and PLB Master Read SERR | |

| interrupt asserted | interrupt asserted | |

|

|

| |

PLB PCI Bridge Master abort | PLB IPIF timeout and Slv_MErr is | PLB IPIF timeout and Slv_MErr is | |

(no PCI target response) | asserted | asserted | |

|

|

| |

Target disconnect without data | Immediate automatic retry | Immediate automatic retry | |

(PCI Retry) | |||

|

| ||

|

|

| |

Target disconnect without data |

| Data is being buffered in PLB PCI | |

(after one completed data | N/A | Bridge PCI2IPIF FIFO. The PCI | |

phase) |

| transaction is terminated by the | |

|

| disconnect. At a parameterized FIFO | |

|

| ||

|

| occupancy level, the PLB PCI Bridge | |

|

| issues another PCI transaction at | |

Target disconnect with data | Completes | correct address. If a PCI retry is | |

asserted, the PCI read automatically | |||

|

| retried. The bridge inhibits IPIF | |

|

| timeout while trying to get the | |

|

| requested data. | |

|

|

| |

| Data is transferred and the PLB | Data transfer to IPIF is stopped, an | |

| IPIF timeout is allowed which results | ||

PERR | Master Read PERR interrupt | ||

in Slv Err asserted and PLB Master | |||

| asserted | ||

| Read PERR interrupt is asserted | ||

|

| ||

|

|

| |

Latency timer expiration | N/A because v3.0 core waits for one | Same as target disconnect | |

transfer after timeout occurs | with/without data | ||

| |||

|

|

| |

| Immediately allow PLB IPIF timeout | Data transfer to IPIF is stopped, | |

| immediately allow PLB IPIF timeout | ||

| which results in Slv_MErr being | ||

Target Abort | which results in Slv_MErr being | ||

asserted and set the PLB Target | |||

| asserted and assert the PLB Target | ||

| Abort Master Read interrupt | ||

| Abort Master Read interrupt | ||

|

| ||

|

|

| |

|

| Stop PCI transaction after last valid | |

|

| address; allow data transfer to IPIF to | |

Address increments beyond | N/A | continue. IPIF timeout and assertion | |

valid range | of Slv_MErr occurs if the PLB master | ||

| |||

|

| request continues when FIFO is | |

|

| empty. | |

|

|

|

PLB Master Initiates a Write Request to a PCI Target

This section discusses the operation of an PLB master initiating single, burst and cache line write transactions to a remote PCI target. All PLB write transactions are

DS508 March 21, 2006 | www.xilinx.com | 37 |

Product Specification