PLB PCI Full Bridge (v1.00a)

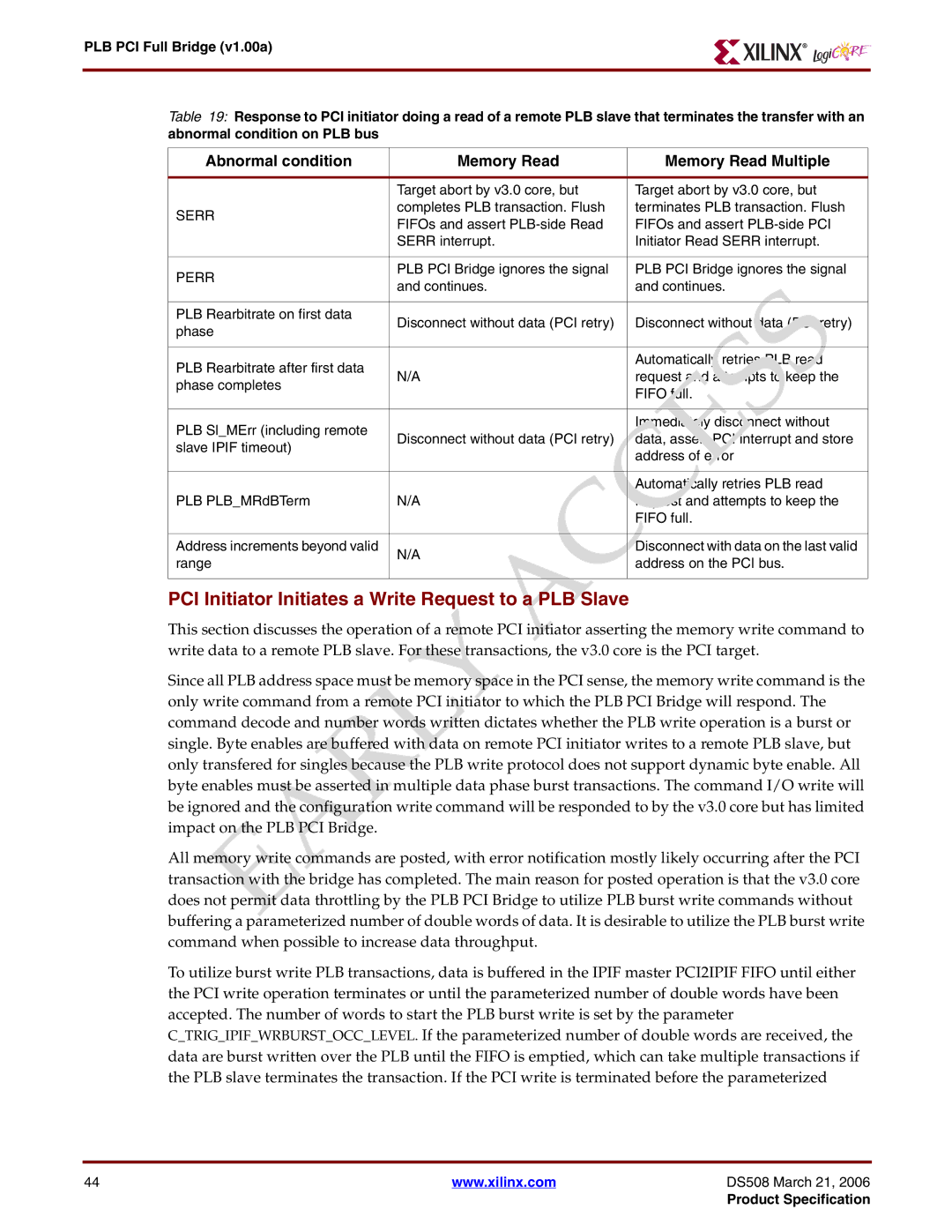

Table 19: Response to PCI initiator doing a read of a remote PLB slave that terminates the transfer with an abnormal condition on PLB bus

Abnormal condition | Memory Read | Memory Read Multiple | |

|

|

| |

| Target abort by v3.0 core, but | Target abort by v3.0 core, but | |

SERR | completes PLB transaction. Flush | terminates PLB transaction. Flush | |

FIFOs and assert | FIFOs and assert | ||

| |||

| SERR interrupt. | Initiator Read SERR interrupt. | |

|

|

| |

PERR | PLB PCI Bridge ignores the signal | PLB PCI Bridge ignores the signal | |

and continues. | and continues. | ||

| |||

|

|

| |

PLB Rearbitrate on first data | Disconnect without data (PCI retry) | Disconnect without data (PCI retry) | |

phase | |||

|

| ||

|

|

| |

PLB Rearbitrate after first data |

| Automatically retries PLB read | |

N/A | request and attempts to keep the | ||

phase completes | |||

| FIFO full. | ||

|

| ||

|

|

| |

PLB Sl_MErr (including remote |

| Immediately disconnect without | |

Disconnect without data (PCI retry) | data, assert PCI interrupt and store | ||

slave IPIF timeout) | |||

| address of error | ||

|

| ||

|

|

| |

|

| Automatically retries PLB read | |

PLB PLB_MRdBTerm | N/A | request and attempts to keep the | |

|

| FIFO full. | |

|

|

| |

Address increments beyond valid | N/A | Disconnect with data on the last valid | |

range | address on the PCI bus. | ||

| |||

|

|

|

PCI Initiator Initiates a Write Request to a PLB Slave

This section discusses the operation of a remote PCI initiator asserting the memory write command to write data to a remote PLB slave. For these transactions, the v3.0 core is the PCI target.

Since all PLB address space must be memory space in the PCI sense, the memory write command is the only write command from a remote PCI initiator to which the PLB PCI Bridge will respond. The command decode and number words written dictates whether the PLB write operation is a burst or single. Byte enables are buffered with data on remote PCI initiator writes to a remote PLB slave, but only transfered for singles because the PLB write protocol does not support dynamic byte enable. All byte enables must be asserted in multiple data phase burst transactions. The command I/O write will be ignored and the configuration write command will be responded to by the v3.0 core but has limited impact on the PLB PCI Bridge.

All memory write commands are posted, with error notification mostly likely occurring after the PCI transaction with the bridge has completed. The main reason for posted operation is that the v3.0 core does not permit data throttling by the PLB PCI Bridge to utilize PLB burst write commands without buffering a parameterized number of double words of data. It is desirable to utilize the PLB burst write command when possible to increase data throughput.

To utilize burst write PLB transactions, data is buffered in the IPIF master PCI2IPIF FIFO until either the PCI write operation terminates or until the parameterized number of double words have been accepted. The number of words to start the PLB burst write is set by the parameter C_TRIG_IPIF_WRBURST_OCC_LEVEL. If the parameterized number of double words are received, the data are burst written over the PLB until the FIFO is emptied, which can take multiple transactions if the PLB slave terminates the transaction. If the PCI write is terminated before the parameterized

44 | www.xilinx.com | DS508 March 21, 2006 |

|

| Product Specification |