|

|

|

|

|

| PLB PCI Full Bridge (v1.00a) |

|

|

|

|

|

|

|

|

| Table 4: Supported PCI Bus Commands |

|

| ||

|

|

|

|

|

| |

|

|

| 1101 | Dual Address Cycle | Ignore | No |

|

|

|

|

|

|

|

|

|

| 1110 | Memory Read Line | Yes | No |

|

|

|

|

|

|

|

|

|

| 1111 | Memory Write Invalidate | Yes | No |

|

|

|

|

|

|

|

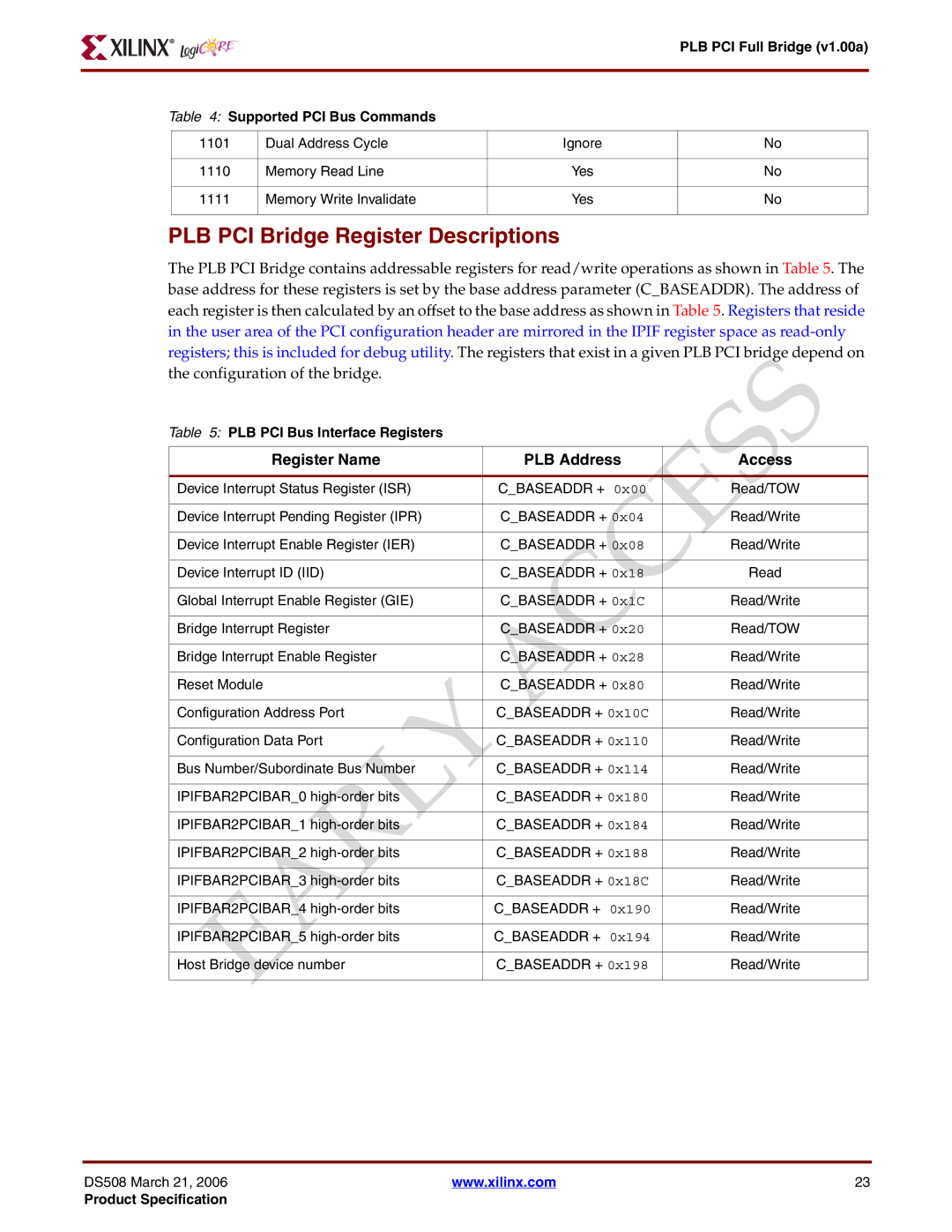

PLB PCI Bridge Register Descriptions

The PLB PCI Bridge contains addressable registers for read/write operations as shown in Table 5. The base address for these registers is set by the base address parameter (C_BASEADDR). The address of each register is then calculated by an offset to the base address as shown in Table 5. Registers that reside in the user area of the PCI configuration header are mirrored in the IPIF register space as

Table 5: PLB PCI Bus Interface Registers

Register Name | PLB Address | Access | |

|

|

|

|

Device Interrupt Status Register (ISR) | C BASEADDR + | 0x00 | Read/TOW |

|

|

| |

Device Interrupt Pending Register (IPR) | C BASEADDR + 0x04 | Read/Write | |

|

|

| |

Device Interrupt Enable Register (IER) | C BASEADDR + 0x08 | Read/Write | |

|

|

| |

Device Interrupt ID (IID) | C BASEADDR + 0x18 | Read | |

|

|

| |

Global Interrupt Enable Register (GIE) | C BASEADDR + 0x1C | Read/Write | |

|

|

| |

Bridge Interrupt Register | C BASEADDR + 0x20 | Read/TOW | |

|

|

| |

Bridge Interrupt Enable Register | C BASEADDR + 0x28 | Read/Write | |

|

|

| |

Reset Module | C BASEADDR + 0x80 | Read/Write | |

|

|

| |

Configuration Address Port | C BASEADDR + 0x10C | Read/Write | |

|

|

| |

Configuration Data Port | C_BASEADDR + 0x110 | Read/Write | |

|

|

| |

Bus Number/Subordinate Bus Number | C_BASEADDR + 0x114 | Read/Write | |

|

|

| |

IPIFBAR2PCIBAR_0 | C_BASEADDR + 0x180 | Read/Write | |

|

|

| |

IPIFBAR2PCIBAR 1 | C_BASEADDR + 0x184 | Read/Write | |

|

|

| |

IPIFBAR2PCIBAR 2 | C_BASEADDR + 0x188 | Read/Write | |

|

|

| |

IPIFBAR2PCIBAR 3 | C_BASEADDR + 0x18C | Read/Write | |

|

|

|

|

IPIFBAR2PCIBAR 4 | C_BASEADDR + | 0x190 | Read/Write |

|

|

|

|

IPIFBAR2PCIBAR 5 | C_BASEADDR + | 0x194 | Read/Write |

|

|

| |

Host Bridge device number | C_BASEADDR + 0x198 | Read/Write | |

|

|

|

|

DS508 March 21, 2006 | www.xilinx.com | 23 |

Product Specification