PLB PCI Full Bridge (v1.00a)

subordinate buses. Device numbers are independent for each PLB PCI bridge instantiated, but bus numbering must be monotonically increasing for all primary buses and their subordinate buses.

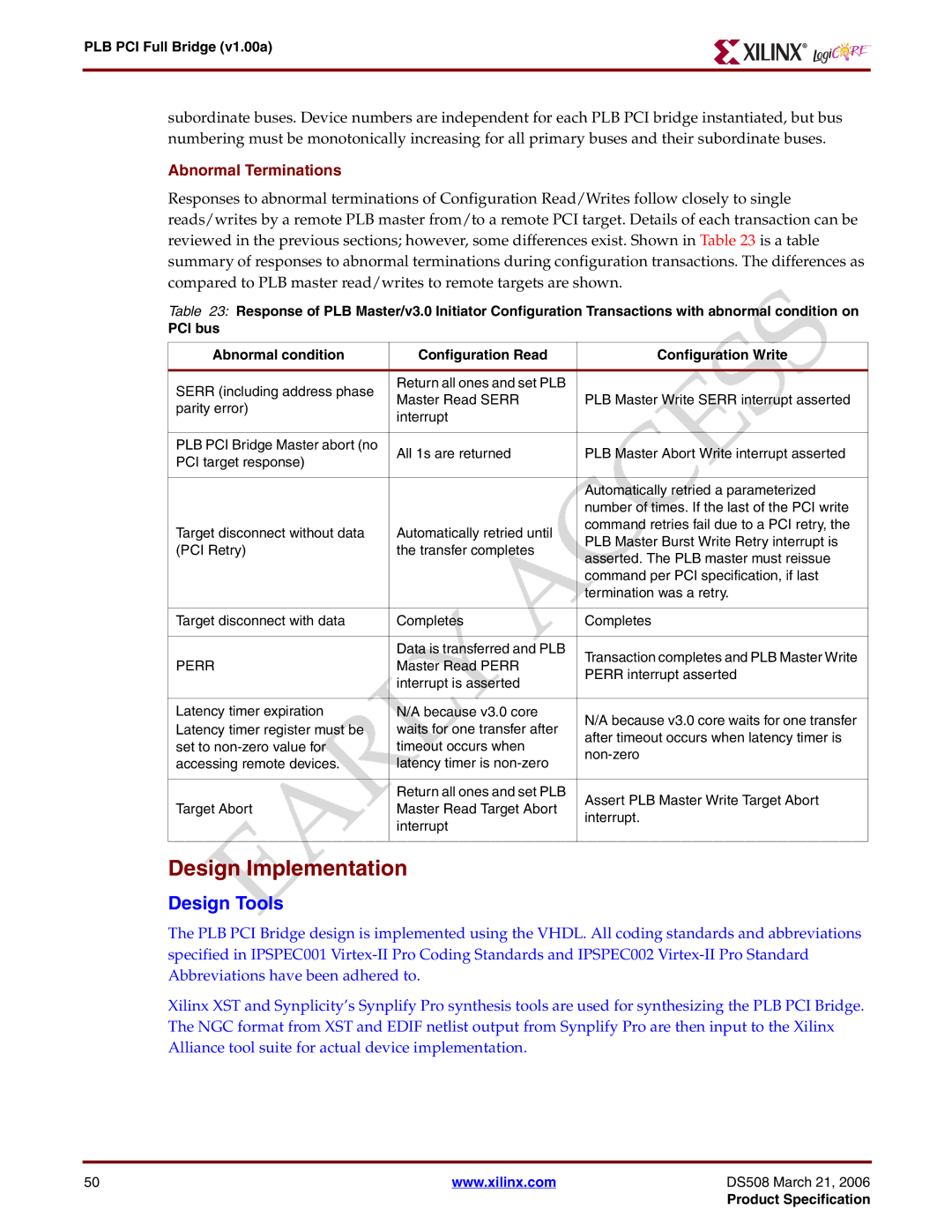

Abnormal Terminations

Responses to abnormal terminations of Configuration Read/Writes follow closely to single reads/writes by a remote PLB master from/to a remote PCI target. Details of each transaction can be reviewed in the previous sections; however, some differences exist. Shown in Table 23 is a table summary of responses to abnormal terminations during configuration transactions. The differences as compared to PLB master read/writes to remote targets are shown.

Table 23: Response of PLB Master/v3.0 Initiator Configuration Transactions with abnormal condition on

PCI bus

Abnormal condition | Configuration Read | Configuration Write | |

|

|

| |

SERR (including address phase | Return all ones and set PLB |

| |

Master Read SERR | PLB Master Write SERR interrupt asserted | ||

parity error) | |||

interrupt |

| ||

|

| ||

|

|

| |

PLB PCI Bridge Master abort (no | All 1s are returned | PLB Master Abort Write interrupt asserted | |

PCI target response) | |||

|

| ||

|

|

| |

|

| Automatically retried a parameterized | |

|

| number of times. If the last of the PCI write | |

Target disconnect without data | Automatically retried until | command retries fail due to a PCI retry, the | |

PLB Master Burst Write Retry interrupt is | |||

(PCI Retry) | the transfer completes | ||

asserted. The PLB master must reissue | |||

|

| ||

|

| command per PCI specification, if last | |

|

| termination was a retry. | |

|

|

| |

Target disconnect with data | Completes | Completes | |

|

|

| |

| Data is transferred and PLB | Transaction completes and PLB Master Write | |

PERR | Master Read PERR | ||

PERR interrupt asserted | |||

| interrupt is asserted | ||

|

| ||

|

|

| |

Latency timer expiration | N/A because v3.0 core | N/A because v3.0 core waits for one transfer | |

Latency timer register must be | waits for one transfer after | ||

after timeout occurs when latency timer is | |||

set to | timeout occurs when | ||

accessing remote devices. | latency timer is | ||

| |||

|

|

| |

| Return all ones and set PLB | Assert PLB Master Write Target Abort | |

Target Abort | Master Read Target Abort | ||

interrupt. | |||

| interrupt | ||

|

| ||

|

|

|

Design Implementation

Design Tools

The PLB PCI Bridge design is implemented using the VHDL. All coding standards and abbreviations specified in IPSPEC001

Xilinx XST and Synplicity’s Synplify Pro synthesis tools are used for synthesizing the PLB PCI Bridge. The NGC format from XST and EDIF netlist output from Synplify Pro are then input to the Xilinx Alliance tool suite for actual device implementation.

50 | www.xilinx.com | DS508 March 21, 2006 |

|

| Product Specification |