PLB PCI Full Bridge (v1.00a)

Register and Parameter Dependencies

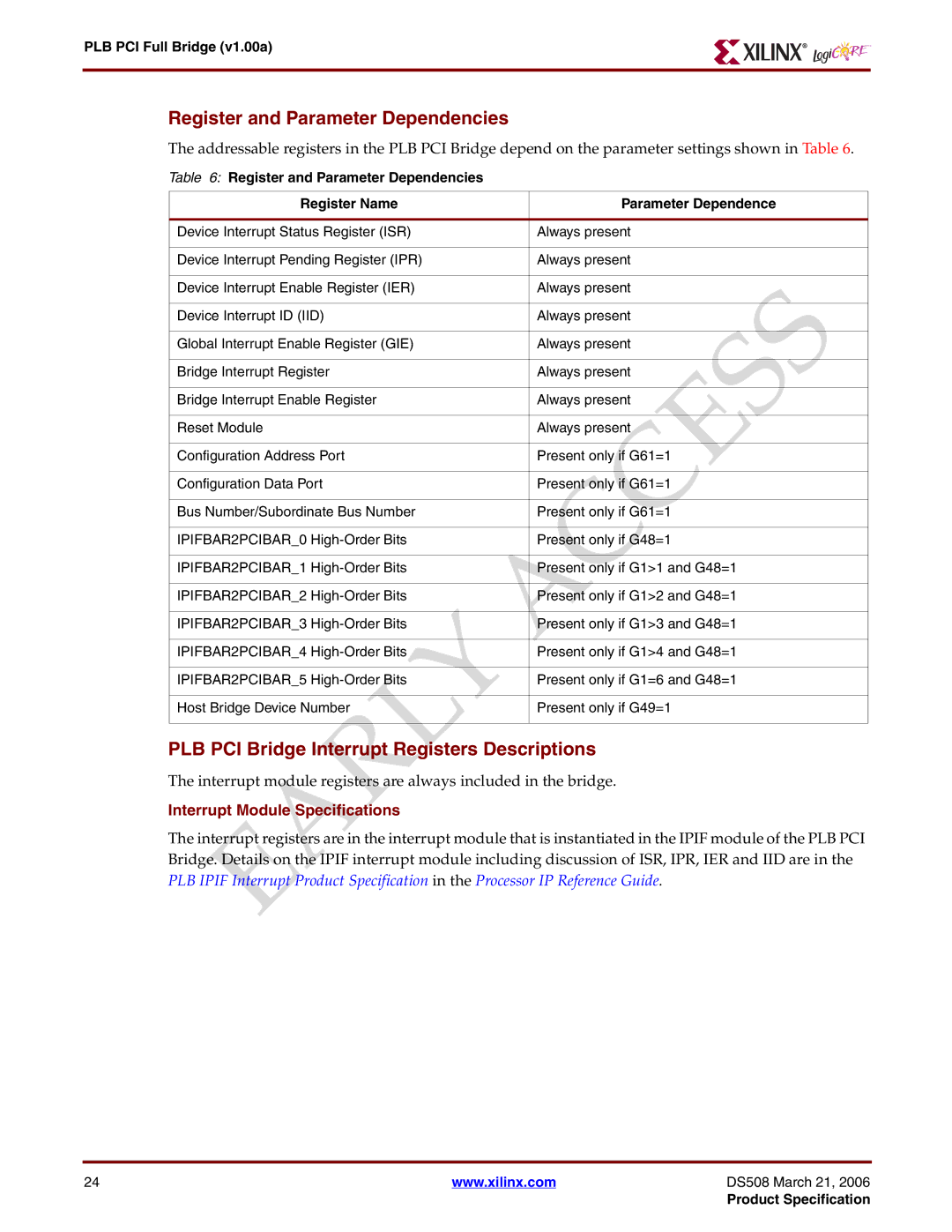

The addressable registers in the PLB PCI Bridge depend on the parameter settings shown in Table 6.

Table 6: Register and Parameter Dependencies

Register Name | Parameter Dependence |

|

|

Device Interrupt Status Register (ISR) | Always present |

|

|

Device Interrupt Pending Register (IPR) | Always present |

|

|

Device Interrupt Enable Register (IER) | Always present |

|

|

Device Interrupt ID (IID) | Always present |

|

|

Global Interrupt Enable Register (GIE) | Always present |

|

|

Bridge Interrupt Register | Always present |

|

|

Bridge Interrupt Enable Register | Always present |

|

|

Reset Module | Always present |

|

|

Configuration Address Port | Present only if G61=1 |

|

|

Configuration Data Port | Present only if G61=1 |

|

|

Bus Number/Subordinate Bus Number | Present only if G61=1 |

|

|

IPIFBAR2PCIBAR_0 | Present only if G48=1 |

|

|

IPIFBAR2PCIBAR_1 | Present only if G1>1 and G48=1 |

|

|

IPIFBAR2PCIBAR_2 | Present only if G1>2 and G48=1 |

|

|

IPIFBAR2PCIBAR_3 | Present only if G1>3 and G48=1 |

|

|

IPIFBAR2PCIBAR 4 | Present only if G1>4 and G48=1 |

|

|

IPIFBAR2PCIBAR 5 | Present only if G1=6 and G48=1 |

|

|

Host Bridge Device Number | Present only if G49=1 |

|

|

PLB PCI Bridge Interrupt Registers Descriptions

The interrupt module registers are always included in the bridge.

Interrupt Module Specifications

The interrupt registers are in the interrupt module that is instantiated in the IPIF module of the PLB PCI Bridge. Details on the IPIF interrupt module including discussion of ISR, IPR, IER and IID are in the PLB IPIF Interrupt Product Specification in the Processor IP Reference Guide.

24 | www.xilinx.com | DS508 March 21, 2006 |

|

| Product Specification |