PLB PCI Full Bridge (v1.00a)

transaction. The PLB PCI Bridge performs retries up to a parameterized number of times as described earlier for the condition of disconnects with/without data. A

•If a target abort occurs during either a single or burst write operation, the PLB Master Write Target Abort interrupt is asserted. If a burst write is in progress, Sl_MErr is asserted with Sl_wrDAck. Recall that a target abort often indicates that the target cannot proceed with subsequent transactions; this is expected to be a major failure most likely requiring a reset.

•If the remote PLB master burst writes beyond a valid address range, the PLB IPIF will accept the data because the PLB IPIF does not check for valid address with data phase. However, the PLB PCI Bridge will not accept the data and the data will remain buffered in the PLB IPIF. In this situation, a PLB IPIF timeout will occur for each double word buffered in the IPIF. Because the write is posted, the PLB transaction has completed on the PLB and Slv MErr is not asserted. When each timeout occurs, the double word presented at the IPIC is discarded and the next double word is presented at the IPIC. After the last timeout occurs and the last valid data is transferred successfully to the PCI target, the bridge is available for a new write transaction.

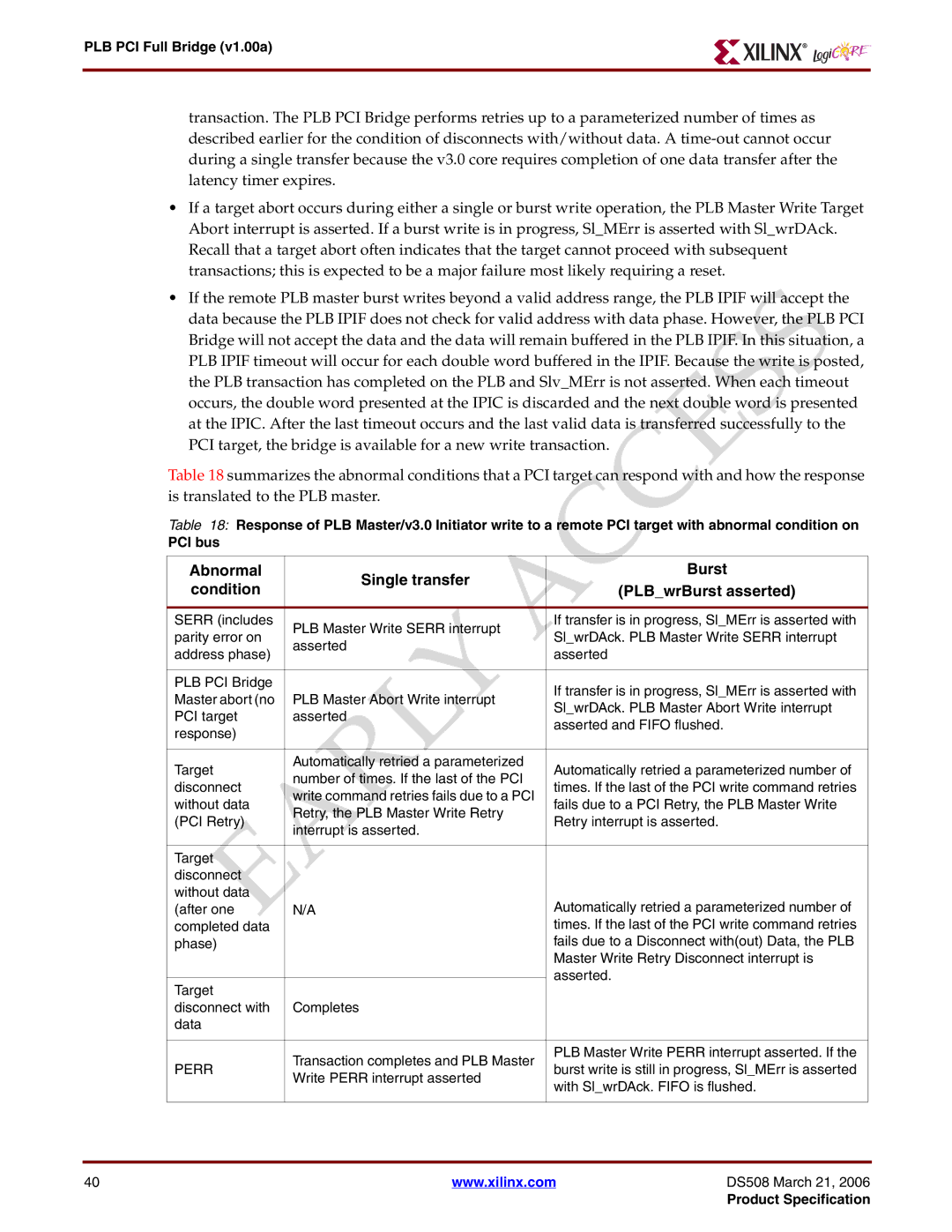

Table 18 summarizes the abnormal conditions that a PCI target can respond with and how the response is translated to the PLB master.

Table 18: Response of PLB Master/v3.0 Initiator write to a remote PCI target with abnormal condition on

PCI bus

Abnormal | Single transfer | Burst | |

condition | (PLB wrBurst asserted) | ||

| |||

|

|

| |

SERR (includes | PLB Master Write SERR interrupt | If transfer is in progress, Sl MErr is asserted with | |

parity error on | Sl wrDAck. PLB Master Write SERR interrupt | ||

asserted | |||

address phase) | asserted | ||

| |||

|

|

| |

PLB PCI Bridge |

| If transfer is in progress, Sl_MErr is asserted with | |

Master abort (no | PLB Master Abort Write interrupt | ||

Sl_wrDAck. PLB Master Abort Write interrupt | |||

PCI target | asserted | ||

asserted and FIFO flushed. | |||

response) |

| ||

|

| ||

|

|

| |

Target | Automatically retried a parameterized | Automatically retried a parameterized number of | |

number of times. If the last of the PCI | |||

disconnect | times. If the last of the PCI write command retries | ||

write command retries fails due to a PCI | |||

without data | fails due to a PCI Retry, the PLB Master Write | ||

Retry, the PLB Master Write Retry | |||

(PCI Retry) | Retry interrupt is asserted. | ||

interrupt is asserted. | |||

|

| ||

|

|

| |

Target |

|

| |

disconnect |

|

| |

without data |

| Automatically retried a parameterized number of | |

(after one | N/A | ||

completed data |

| times. If the last of the PCI write command retries | |

phase) |

| fails due to a Disconnect with(out) Data, the PLB | |

|

| Master Write Retry Disconnect interrupt is | |

|

| asserted. | |

Target |

| ||

|

| ||

disconnect with | Completes |

| |

data |

|

| |

|

|

| |

| Transaction completes and PLB Master | PLB Master Write PERR interrupt asserted. If the | |

PERR | burst write is still in progress, Sl_MErr is asserted | ||

Write PERR interrupt asserted | |||

| with Sl_wrDAck. FIFO is flushed. | ||

|

| ||

|

|

|

40 | www.xilinx.com | DS508 March 21, 2006 |

|

| Product Specification |