PLB PCI Full Bridge (v1.00a)

The constraints are also implemented automatically in the EDK tool flow with any tool option that invokes bridge synthesis. In this flow,

To remind the user that the following constraints must be included, PLATGEN will generate the message:

The OPB PCI Bridge design requires design constraints to guarantee performance. Please refer to the OPB IPIF/LogiCORE PCI64 v3.0 bridge design data sheet for details.

Additional bridge specific constraints are required and an example

An example UCF is available for this core and must be modified for use in the system. Please refer to the EDK Getting Started guide for the location of this file.

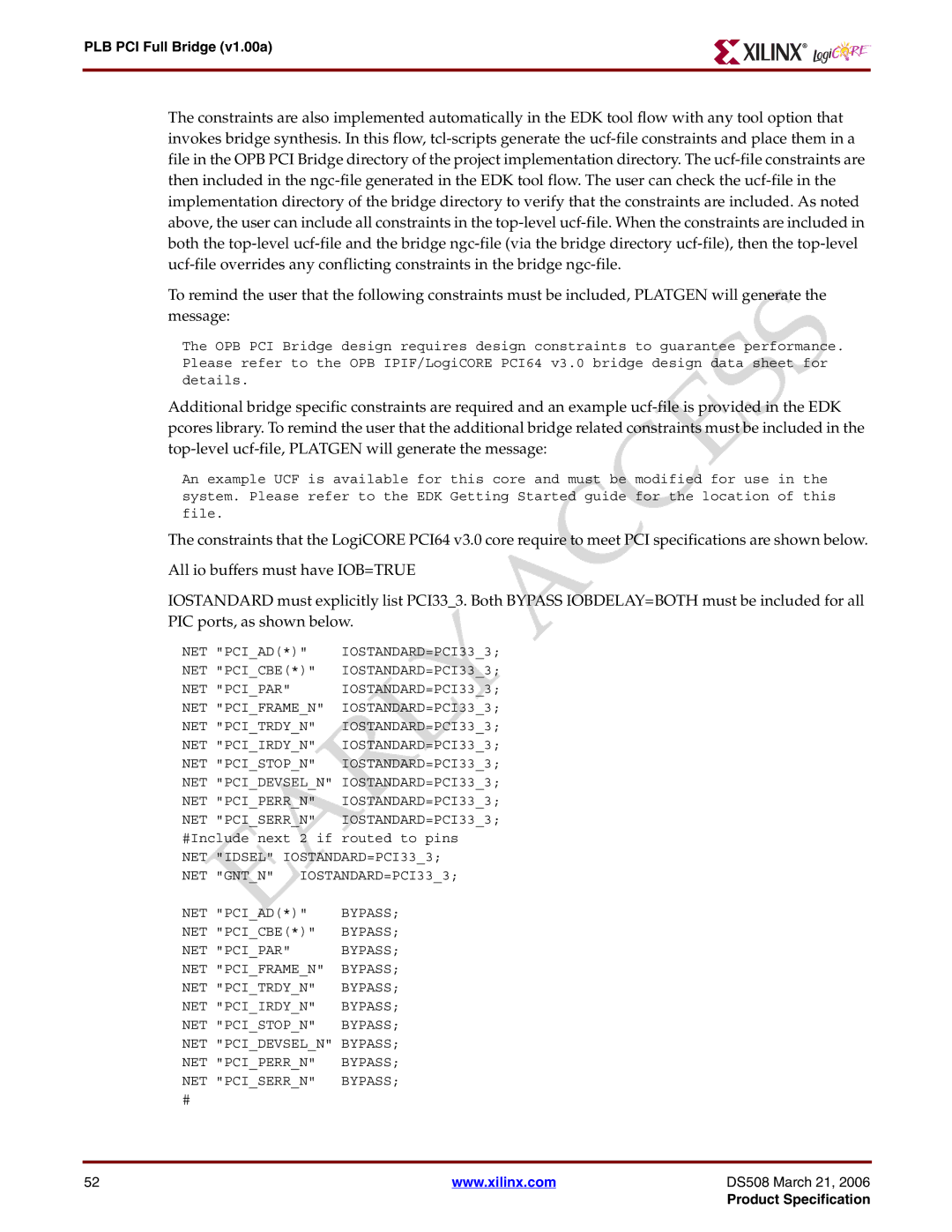

The constraints that the LogiCORE PCI64 v3.0 core require to meet PCI specifications are shown below.

All io buffers must have IOB=TRUE

IOSTANDARD must explicitly list PCI33_3. Both BYPASS IOBDELAY=BOTH must be included for all PIC ports, as shown below.

NET "PCI AD(*)" IOSTANDARD=PCI33 3;

NET "PCI CBE(*)" IOSTANDARD=PCI33 3;

NET "PCI PAR" IOSTANDARD=PCI33 3; NET "PCI FRAME N" IOSTANDARD=PCI33 3; NET "PCI TRDY N" IOSTANDARD=PCI33 3; NET "PCI IRDY N" IOSTANDARD=PCI33 3; NET "PCI STOP N" IOSTANDARD=PCI33 3; NET "PCI DEVSEL N" IOSTANDARD=PCI33 3; NET "PCI PERR N" IOSTANDARD=PCI33 3; NET "PCI SERR N" IOSTANDARD=PCI33 3; #Include next 2 if routed to pins NET "IDSEL" IOSTANDARD=PCI33 3;

NET "GNT N" IOSTANDARD=PCI33 3;

NET "PCI AD(*)" BYPASS;

NET "PCI CBE(*)" BYPASS;

NET "PCI_PAR" BYPASS;

NET "PCI_FRAME_N" BYPASS;

NET "PCI_TRDY_N" BYPASS;

NET "PCI_IRDY_N" BYPASS;

NET "PCI_STOP_N" BYPASS;

NET "PCI_DEVSEL_N" BYPASS;

NET "PCI_PERR_N" BYPASS;

NET "PCI_SERR_N" BYPASS;

#

52 | www.xilinx.com | DS508 March 21, 2006 |

|

| Product Specification |