PLB PCI Full Bridge (v1.00a)

The parameter C_IDELAYCTRL_LOC has the syntax of IDELAYCTRL_XNYM where N and M are coordinates and multiple entries are concatenated by

PARAMETER C_IDELAYCTRL_LOC="IDELAYCTRL_X2Y5-IDELAYCTRL_X2Y6"

The quotes are optional. The actual number of IDELAYCTRL primitives and corresponding LOC constraints depends on the user’s PCI pinout and part used.

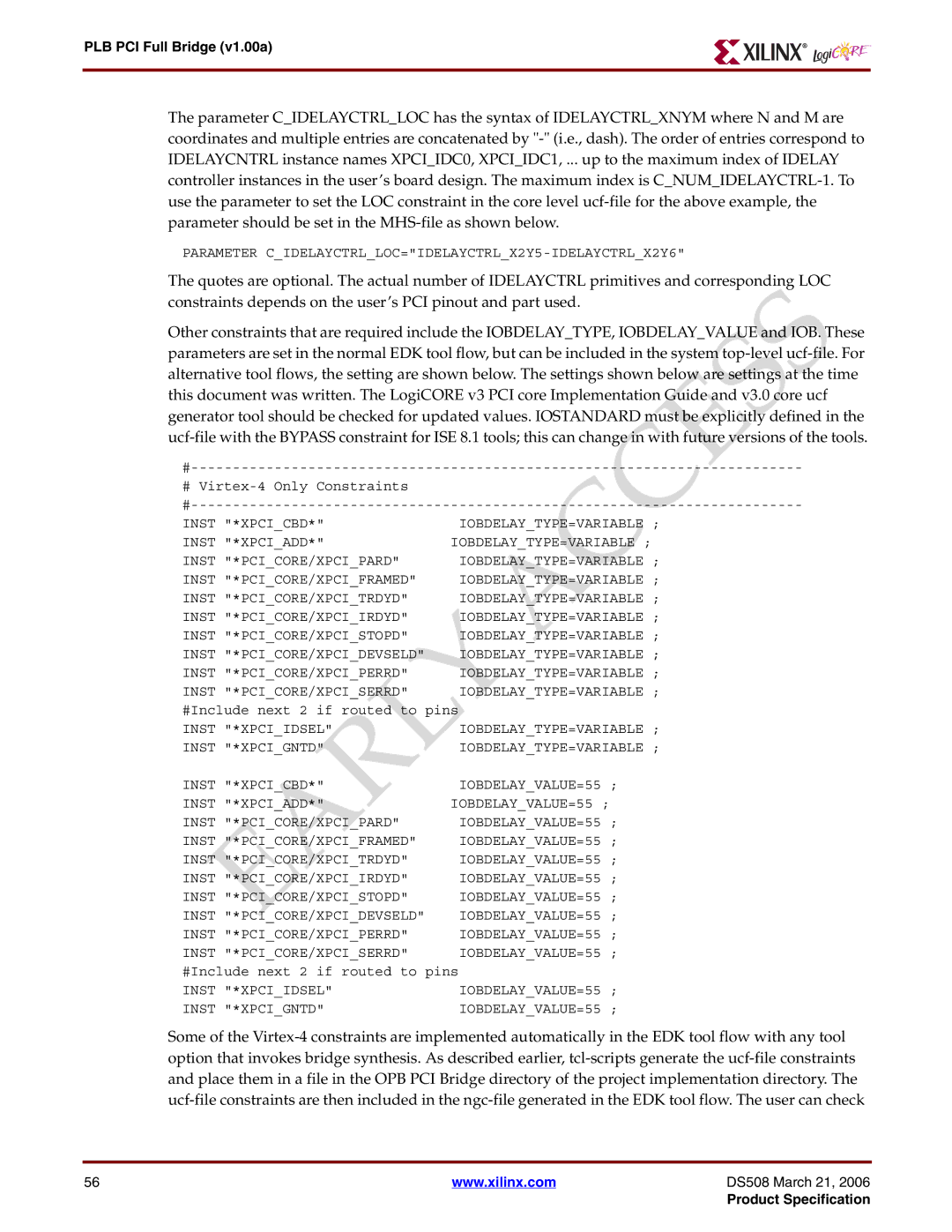

Other constraints that are required include the IOBDELAY TYPE, IOBDELAY VALUE and IOB. These parameters are set in the normal EDK tool flow, but can be included in the system

| ||

# | Only Constraints |

|

| ||

INST "*XPCI_CBD*" | IOBDELAY TYPE=VARIABLE ; | |

INST "*XPCI_ADD*" | IOBDELAY TYPE=VARIABLE ; | |

INST "*PCI_CORE/XPCI_PARD" | IOBDELAY TYPE=VARIABLE ; | |

INST "*PCI_CORE/XPCI_FRAMED" | IOBDELAY TYPE=VARIABLE ; | |

INST "*PCI_CORE/XPCI_TRDYD" | IOBDELAY TYPE=VARIABLE ; | |

INST "*PCI_CORE/XPCI_IRDYD" | IOBDELAY TYPE=VARIABLE ; | |

INST "*PCI_CORE/XPCI_STOPD" | IOBDELAY TYPE=VARIABLE ; | |

INST "*PCI CORE/XPCI DEVSELD" | IOBDELAY TYPE=VARIABLE ; | |

INST "*PCI CORE/XPCI PERRD" | IOBDELAY_TYPE=VARIABLE ; | |

INST "*PCI CORE/XPCI SERRD" | IOBDELAY_TYPE=VARIABLE ; | |

#Include next 2 if routed to pins | ||

INST "*XPCI IDSEL" | IOBDELAY_TYPE=VARIABLE ; | |

INST "*XPCI GNTD" | IOBDELAY_TYPE=VARIABLE ; | |

INST "*XPCI CBD*" | IOBDELAY_VALUE=55 ; | |

INST "*XPCI ADD*" | IOBDELAY_VALUE=55 ; | |

INST "*PCI CORE/XPCI PARD" | IOBDELAY_VALUE=55 ; | |

INST "*PCI CORE/XPCI FRAMED" | IOBDELAY_VALUE=55 ; | |

INST "*PCI CORE/XPCI TRDYD" | IOBDELAY_VALUE=55 ; | |

INST "*PCI CORE/XPCI IRDYD" | IOBDELAY_VALUE=55 ; | |

INST "*PCI CORE/XPCI STOPD" | IOBDELAY_VALUE=55 ; | |

INST "*PCI CORE/XPCI DEVSELD" | IOBDELAY_VALUE=55 ; | |

INST "*PCI CORE/XPCI PERRD" | IOBDELAY_VALUE=55 ; | |

INST "*PCI_CORE/XPCI_SERRD" | IOBDELAY_VALUE=55 ; | |

#Include next 2 if routed to pins | ||

INST "*XPCI_IDSEL" | IOBDELAY_VALUE=55 ; | |

INST "*XPCI_GNTD" | IOBDELAY_VALUE=55 ; | |

Some of the

56 | www.xilinx.com | DS508 March 21, 2006 |

|

| Product Specification |