PLB PCI Full Bridge (v1.00a)

defined number of retries are not successful, the PCI interrupt will be strobed. Data in the write buffer is flushed when the PCI interrupt is strobed.

•If during a write command a PLB slave asserts PLB_MWrBTerm which terminates the PLB burst write, the PLB PCI Bridge automatically retries the PLB request and attempts to empty the fifo. The IPIF will try the number of times given by the parameter C_NUM_IPIF_RETRIES_IN_WRITES and the behavior is the same as that for PLB rearbitrate which is described above. Again, if the

•If at any time while data from the write buffer is being written to a PLB slave a PLB Sl_MErr occurs, the IP Master aborts the PLB transaction. When this occurs, the PLB PCI Bridge strobes the PCI interrupt. Sl_MErr can be asserted due to an address phase timeout or a slave assertion of the error signal. Data in the write buffer is flushed when the PCI interrupt is strobed.

•If on a write command transaction the PCI initiator attempts to go beyond the valid address range, the PLB PCI Bridge will not accept data beyond the valid range. Only valid data is buffered in the bridge and all buffered data will be transferred to the PLB slave. This is adopted rather than a target abort. Due to pipelining in the v3.0 core, disconnect without data can occur if the initiator is throttling the data when the first address is near the end of the valid range.

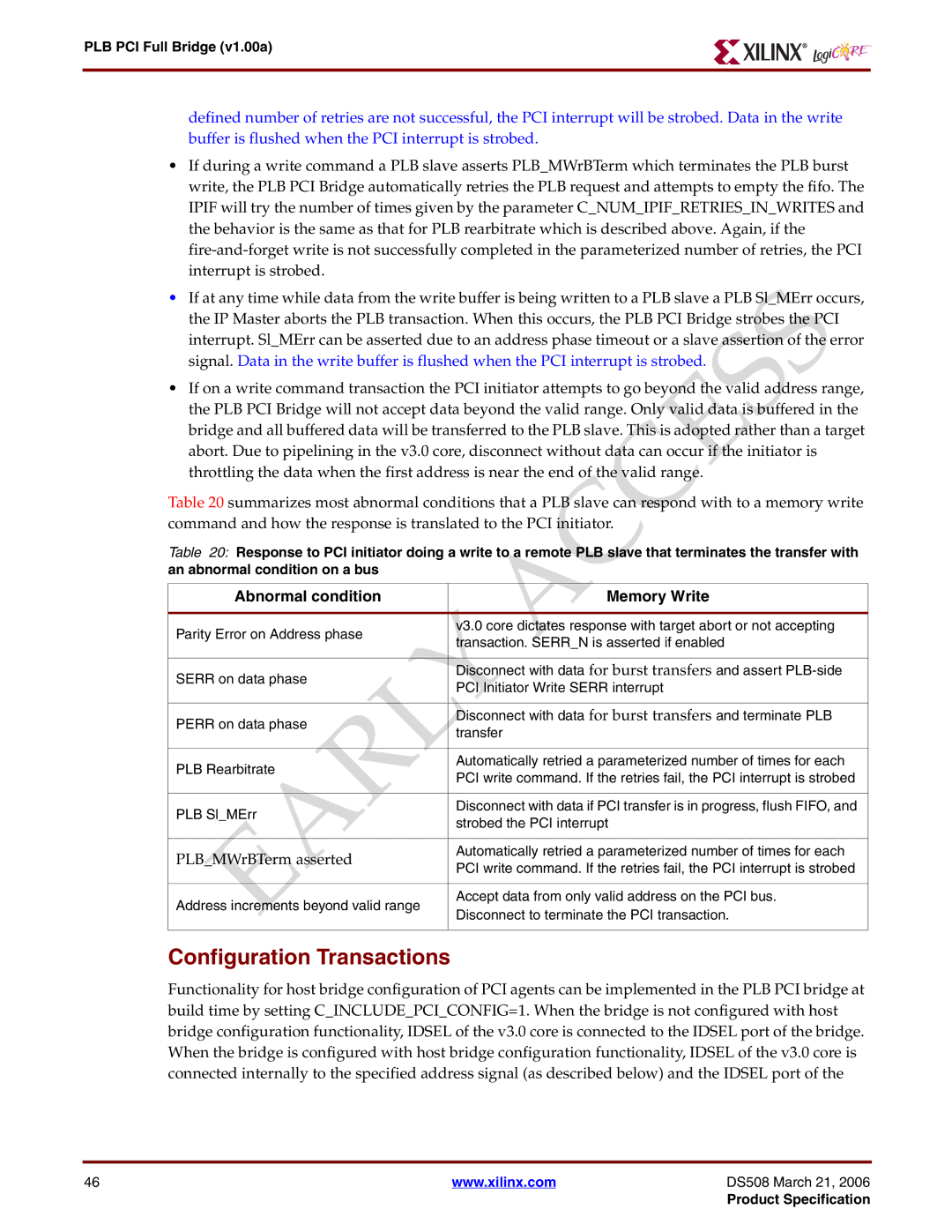

Table 20 summarizes most abnormal conditions that a PLB slave can respond with to a memory write command and how the response is translated to the PCI initiator.

Table 20: Response to PCI initiator doing a write to a remote PLB slave that terminates the transfer with an abnormal condition on a bus

Abnormal condition |

| Memory Write | |

|

| ||

Parity Error on Address phase | v3.0 core dictates response with target abort or not accepting | ||

transaction. SERR | N is asserted if enabled | ||

| |||

|

| ||

SERR on data phase | Disconnect with data for burst transfers and assert | ||

PCI Initiator Write SERR interrupt | |||

| |||

|

| ||

PERR on data phase | Disconnect with data for burst transfers and terminate PLB | ||

transfer |

| ||

|

| ||

|

| ||

PLB Rearbitrate | Automatically retried a parameterized number of times for each | ||

PCI write command. If the retries fail, the PCI interrupt is strobed | |||

| |||

|

| ||

PLB Sl_MErr | Disconnect with data if PCI transfer is in progress, flush FIFO, and | ||

strobed the PCI interrupt | |||

| |||

|

| ||

PLB_MWrBTerm asserted | Automatically retried a parameterized number of times for each | ||

PCI write command. If the retries fail, the PCI interrupt is strobed | |||

| |||

|

| ||

Address increments beyond valid range | Accept data from only valid address on the PCI bus. | ||

Disconnect to terminate the PCI transaction. | |||

| |||

|

|

| |

Configuration Transactions

Functionality for host bridge configuration of PCI agents can be implemented in the PLB PCI bridge at build time by setting C_INCLUDE_PCI_CONFIG=1. When the bridge is not configured with host bridge configuration functionality, IDSEL of the v3.0 core is connected to the IDSEL port of the bridge. When the bridge is configured with host bridge configuration functionality, IDSEL of the v3.0 core is connected internally to the specified address signal (as described below) and the IDSEL port of the

46 | www.xilinx.com | DS508 March 21, 2006 |

|

| Product Specification |