PLB PCI Full Bridge (v1.00a)

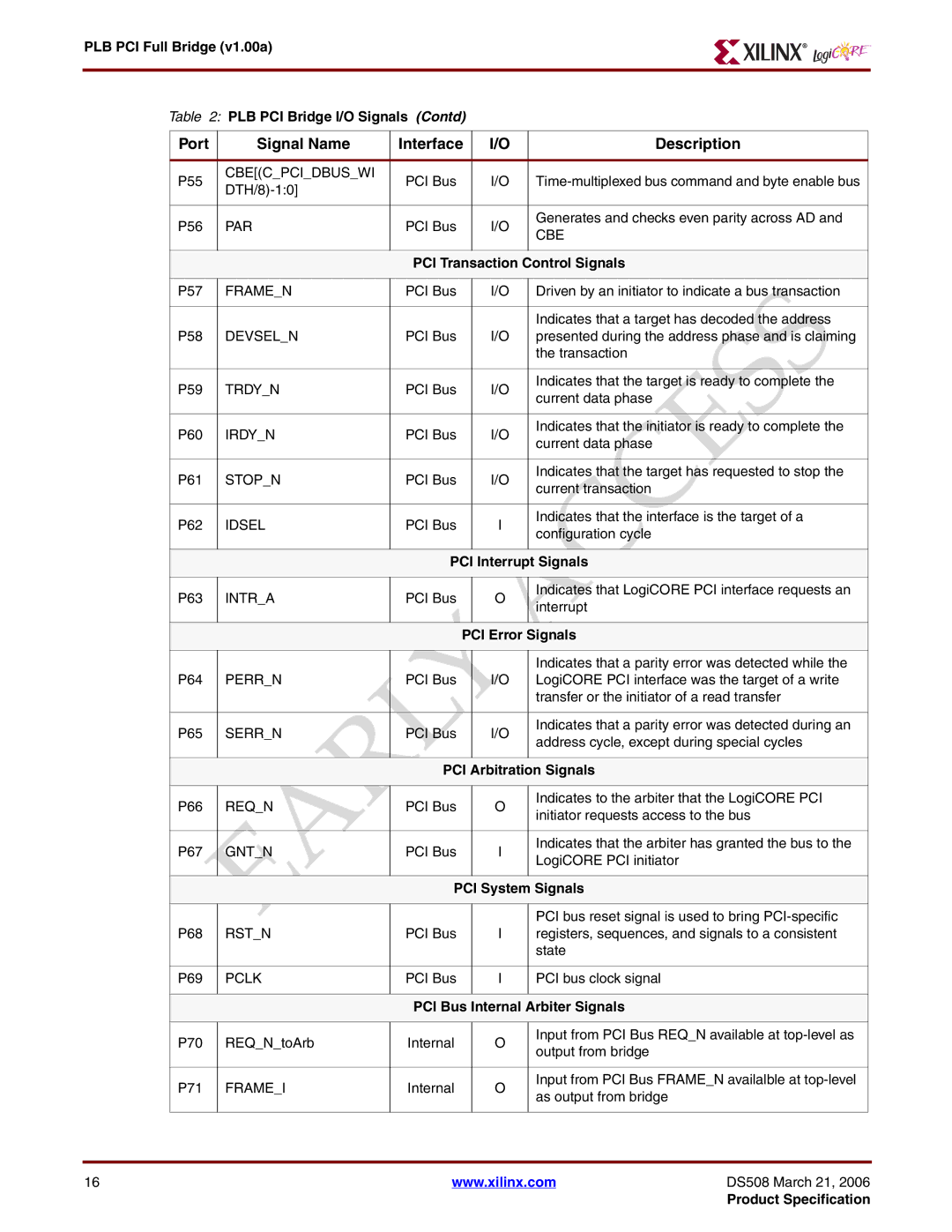

Table 2: | PLB PCI Bridge I/O Signals (Contd) |

|

| |||

|

|

|

|

|

|

|

| Port |

| Signal Name | Interface | I/O | Description |

|

|

|

|

|

|

|

| P55 |

| CBE[(C_PCI_DBUS_WI | PCI Bus | I/O | |

|

| |||||

|

|

|

|

|

| |

|

|

|

|

|

|

|

| P56 |

| PAR | PCI Bus | I/O | Generates and checks even parity across AD and |

|

| CBE | ||||

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| PCI Transaction Control Signals | ||

|

|

|

|

|

|

|

| P57 |

| FRAME_N | PCI Bus | I/O | Driven by an initiator to indicate a bus transaction |

|

|

|

|

|

|

|

|

|

|

|

|

| Indicates that a target has decoded the address |

| P58 |

| DEVSEL_N | PCI Bus | I/O | presented during the address phase and is claiming |

|

|

|

|

|

| the transaction |

|

|

|

|

|

|

|

| P59 |

| TRDY_N | PCI Bus | I/O | Indicates that the target is ready to complete the |

|

| current data phase | ||||

|

|

|

|

|

| |

|

|

|

|

|

|

|

| P60 |

| IRDY_N | PCI Bus | I/O | Indicates that the initiator is ready to complete the |

|

| current data phase | ||||

|

|

|

|

|

| |

|

|

|

|

|

|

|

| P61 |

| STOP_N | PCI Bus | I/O | Indicates that the target has requested to stop the |

|

| current transaction | ||||

|

|

|

|

|

| |

|

|

|

|

|

|

|

| P62 |

| IDSEL | PCI Bus | I | Indicates that the interface is the target of a |

|

| configuration cycle | ||||

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| PCI Interrupt Signals | ||

|

|

|

|

|

|

|

| P63 |

| INTR_A | PCI Bus | O | Indicates that LogiCORE PCI interface requests an |

|

| interrupt | ||||

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| PCI Error Signals | ||

|

|

|

|

|

|

|

|

|

|

|

|

| Indicates that a parity error was detected while the |

| P64 |

| PERR N | PCI Bus | I/O | LogiCORE PCI interface was the target of a write |

|

|

|

|

|

| transfer or the initiator of a read transfer |

|

|

|

|

|

|

|

| P65 |

| SERR N | PCI Bus | I/O | Indicates that a parity error was detected during an |

|

| address cycle, except during special cycles | ||||

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| PCI Arbitration Signals | ||

|

|

|

|

|

|

|

| P66 |

| REQ N | PCI Bus | O | Indicates to the arbiter that the LogiCORE PCI |

|

| initiator requests access to the bus | ||||

|

|

|

|

|

| |

|

|

|

|

|

|

|

| P67 |

| GNT N | PCI Bus | I | Indicates that the arbiter has granted the bus to the |

|

| LogiCORE PCI initiator | ||||

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| PCI System Signals | ||

|

|

|

|

|

|

|

|

|

|

|

|

| PCI bus reset signal is used to bring |

| P68 |

| RST N | PCI Bus | I | registers, sequences, and signals to a consistent |

|

|

|

|

|

| state |

|

|

|

|

|

|

|

| P69 |

| PCLK | PCI Bus | I | PCI bus clock signal |

|

|

|

|

|

|

|

|

|

|

| PCI Bus Internal Arbiter Signals | ||

|

|

|

|

|

|

|

| P70 |

| REQ_N_toArb | Internal | O | Input from PCI Bus REQ_N available at |

|

| output from bridge | ||||

|

|

|

|

|

| |

|

|

|

|

|

|

|

| P71 |

| FRAME_I | Internal | O | Input from PCI Bus FRAME_N availalble at |

|

| as output from bridge | ||||

|

|

|

|

|

| |

|

|

|

|

|

|

|

16 | www.xilinx.com | DS508 March 21, 2006 |

|

| Product Specification |