|

|

|

|

|

|

|

|

| PLB PCI Full Bridge (v1.00a) | |

|

|

|

|

|

|

|

|

|

| |

|

|

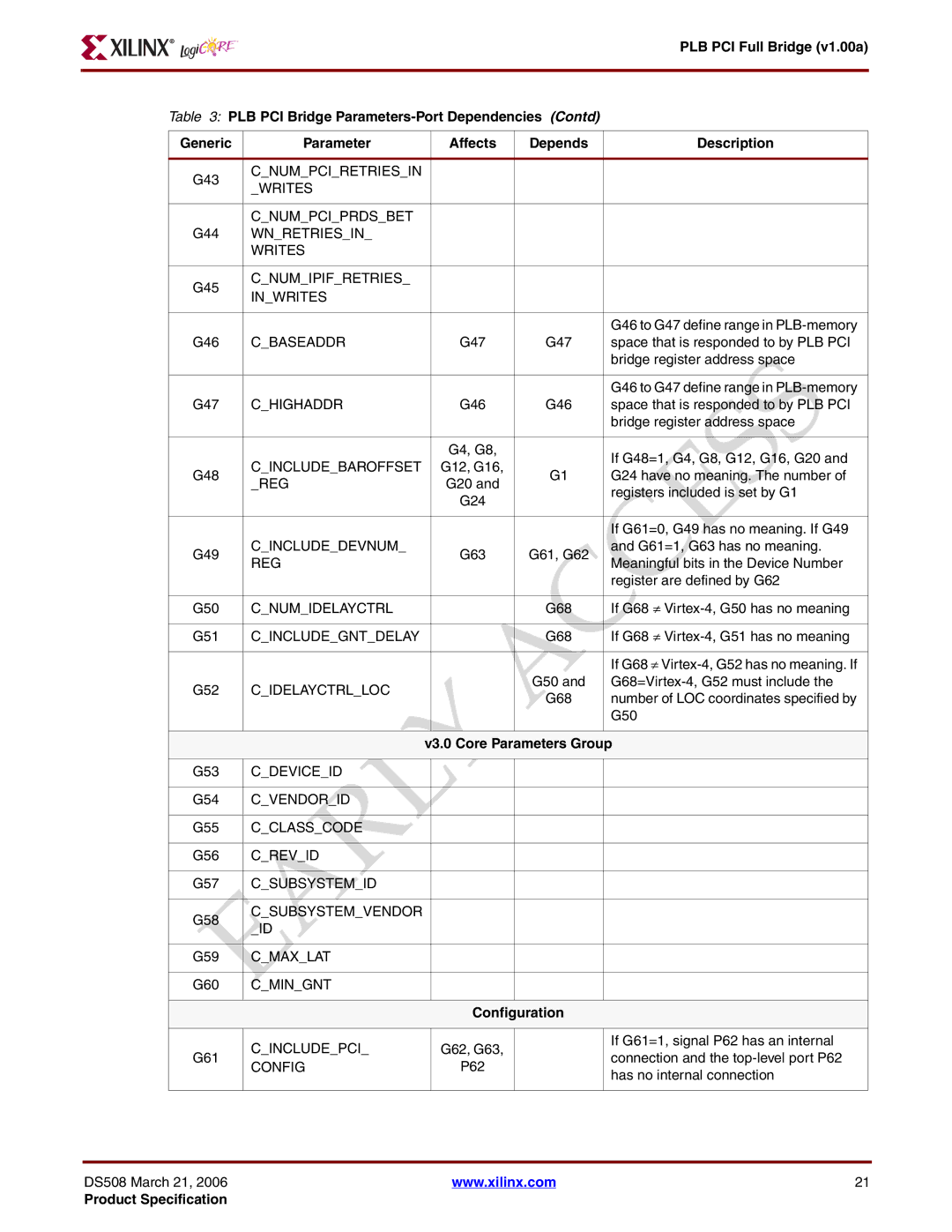

| Table 3: PLB PCI Bridge |

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Generic | Parameter |

| Affects | Depends | Description |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G43 | C_NUM_PCI_RETRIES_IN |

|

|

|

|

|

|

|

|

| _WRITES |

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C_NUM_PCI_PRDS_BET |

|

|

|

|

|

|

|

|

| G44 | WN_RETRIES_IN_ |

|

|

|

|

|

|

|

|

|

| WRITES |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G45 | C_NUM_IPIF_RETRIES_ |

|

|

|

|

|

|

|

|

| IN_WRITES |

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G46 to G47 define range in |

|

|

|

|

| G46 | C_BASEADDR |

| G47 | G47 | space that is responded to by PLB PCI |

|

|

|

|

|

|

|

|

|

| bridge register address space |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G46 to G47 define range in |

|

|

|

|

| G47 | C_HIGHADDR |

| G46 | G46 | space that is responded to by PLB PCI |

|

|

|

|

|

|

|

|

|

| bridge register address space |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G4, G8, |

| If G48=1, G4, G8, G12, G16, G20 and |

|

|

|

|

|

| C_INCLUDE_BAROFFSET |

| G12, G16, |

|

| |

|

|

|

| G48 |

| G1 | G24 have no meaning. The number of |

| ||

|

|

|

| _REG |

| G20 and |

| |||

|

|

|

|

|

|

| registers included is set by G1 |

| ||

|

|

|

|

|

|

| G24 |

|

| |

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| If G61=0, G49 has no meaning. If G49 |

|

|

|

|

| G49 | C_INCLUDE_DEVNUM_ |

| G63 | G61, G62 | and G61=1, G63 has no meaning. |

|

|

|

|

| REG |

| Meaningful bits in the Device Number |

| |||

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| register are defined by G62 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G50 | C_NUM_IDELAYCTRL |

|

| G68 | If G68 ≠ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G51 | C_INCLUDE_GNT_DELAY |

|

| G68 | If G68 ≠ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| If G68 ≠ |

|

|

|

|

| G52 | C_IDELAYCTRL_LOC |

|

| G50 and |

| |

|

|

|

|

|

| G68 | number of LOC coordinates specified by |

| ||

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| G50 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| v3.0 Core Parameters Group |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G53 | C_DEVICE_ID |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G54 | C_VENDOR ID |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G55 | C_CLASS CODE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G56 | C_REV ID |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G57 | C_SUBSYSTEM ID |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G58 | C SUBSYSTEM VENDOR |

|

|

|

|

|

|

|

|

| ID |

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G59 | C MAX LAT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G60 | C MIN_GNT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Configuration |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C_INCLUDE_PCI_ |

| G62, G63, |

| If G61=1, signal P62 has an internal |

|

|

|

|

| G61 |

|

| connection and the |

| ||

|

|

|

| CONFIG |

| P62 |

|

| ||

|

|

|

|

|

|

| has no internal connection |

| ||

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| DS508 March 21, 2006 |

|

| www.xilinx.com | 21 | |||||

| Product Specification |

|

|

|

|

|

| |||