PLB PCI Full Bridge (v1.00a)

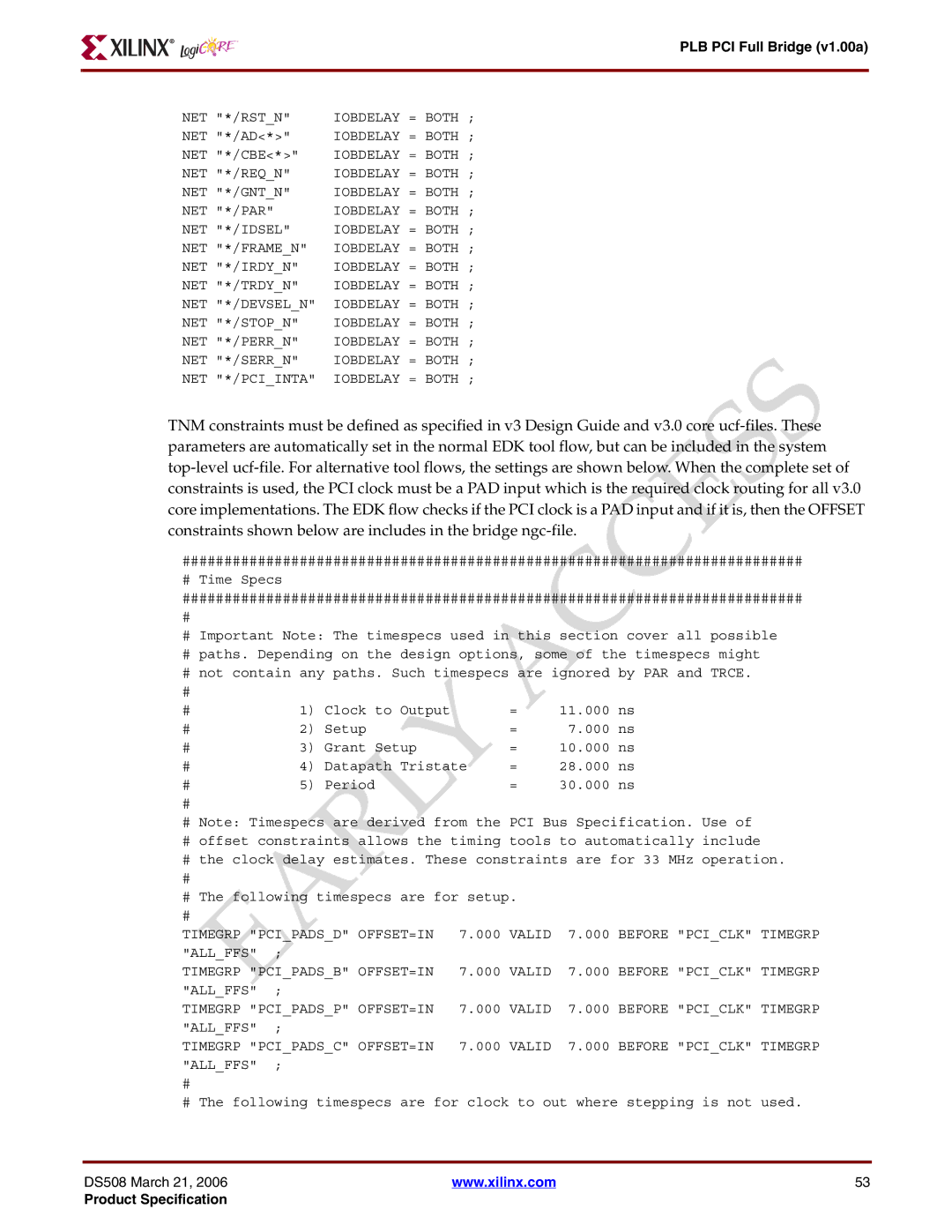

NET "*/RST_N" NET "*/AD<*>" NET "*/CBE<*>" NET "*/REQ_N" NET "*/GNT_N" NET "*/PAR"

NET "*/IDSEL" NET "*/FRAME_N" NET "*/IRDY_N" NET "*/TRDY_N" NET "*/DEVSEL_N" NET "*/STOP_N" NET "*/PERR_N" NET "*/SERR_N" NET "*/PCI_INTA"

IOBDELAY = BOTH ; IOBDELAY = BOTH ; IOBDELAY = BOTH ; IOBDELAY = BOTH ; IOBDELAY = BOTH ; IOBDELAY = BOTH ; IOBDELAY = BOTH ; IOBDELAY = BOTH ; IOBDELAY = BOTH ; IOBDELAY = BOTH ; IOBDELAY = BOTH ; IOBDELAY = BOTH ; IOBDELAY = BOTH ; IOBDELAY = BOTH ; IOBDELAY = BOTH ;

TNM constraints must be defined as specified in v3 Design Guide and v3.0 core

##########################################################################

#Time Specs

##########################################################################

#Important Note: The timespecs used in this section cover all possible

#paths. Depending on the design options, some of the timespecs might

#not contain any paths. Such timespecs are ignored by PAR and TRCE.

# |

|

|

|

|

|

# | 1) | Clock to Output | = | 11.000 | ns |

# | 2) | Setup | = | 7.000 | ns |

# | 3) | Grant Setup | = | 10.000 | ns |

# | 4) | Datapath Tristate | = | 28.000 | ns |

# | 5) | Period | = | 30.000 | ns |

# |

|

|

|

|

|

#Note: Timespecs are derived from the PCI Bus Specification. Use of

#offset constraints allows the timing tools to automatically include

#the clock delay estimates. These constraints are for 33 MHz operation.

#The following timespecs are for setup.

# |

|

|

|

|

|

TIMEGRP "PCI PADS D" OFFSET=IN | 7.000 | VALID | 7.000 | BEFORE "PCI_CLK" TIMEGRP | |

"ALL FFS" | ; |

|

|

|

|

TIMEGRP "PCI_PADS_B" OFFSET=IN | 7.000 | VALID | 7.000 | BEFORE "PCI_CLK" TIMEGRP | |

"ALL FFS" | ; |

|

|

|

|

TIMEGRP "PCI_PADS_P" OFFSET=IN | 7.000 | VALID | 7.000 | BEFORE "PCI_CLK" TIMEGRP | |

"ALL_FFS" | ; |

|

|

|

|

TIMEGRP "PCI_PADS_C" OFFSET=IN | 7.000 | VALID | 7.000 | BEFORE "PCI_CLK" TIMEGRP | |

"ALL_FFS" | ; |

|

|

|

|

#

# The following timespecs are for clock to out where stepping is not used.

DS508 March 21, 2006 | www.xilinx.com | 53 |

Product Specification