PLB PCI Full Bridge (v1.00a)

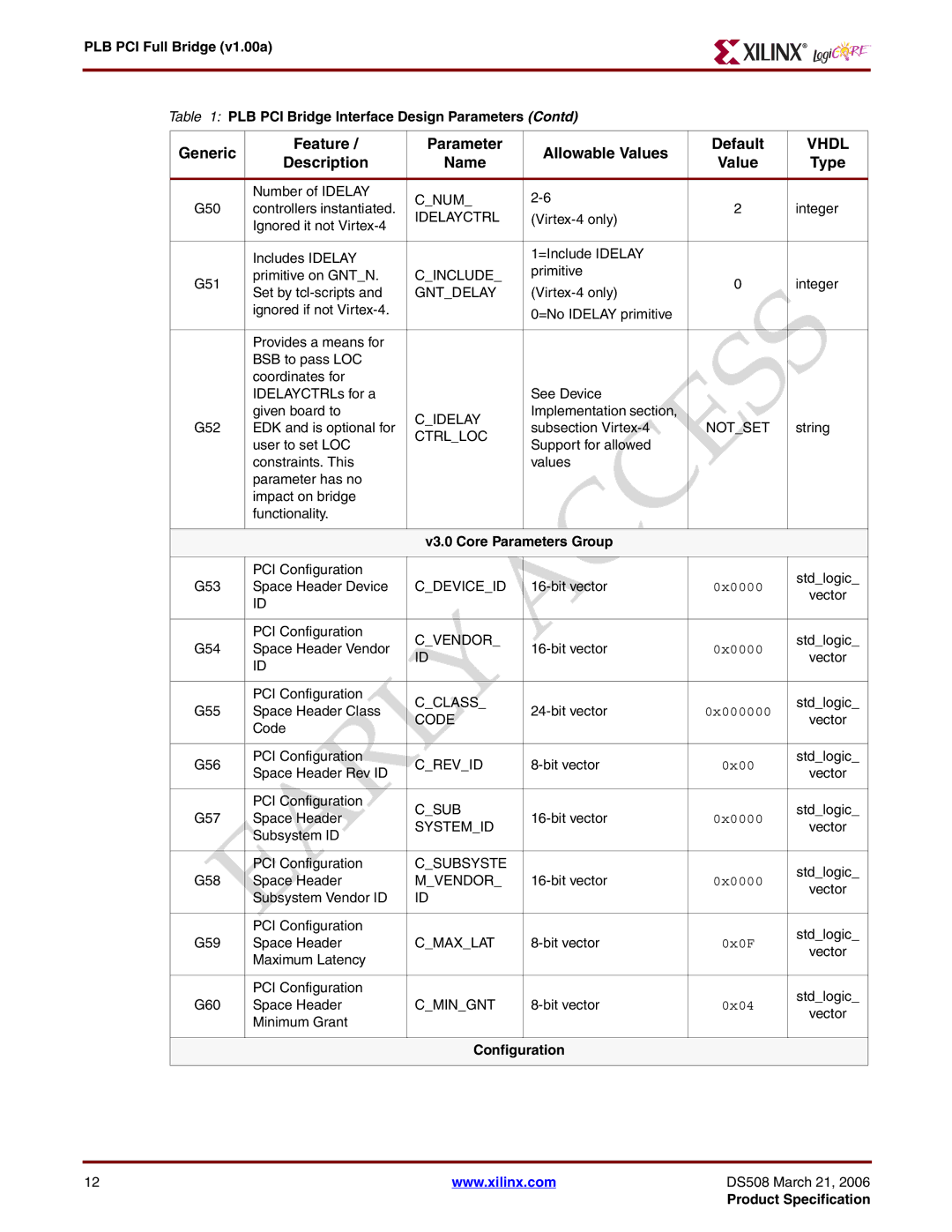

Table 1: PLB PCI Bridge Interface Design Parameters (Contd)

Generic | Feature / | Parameter | Allowable Values | Default | VHDL | |

Description | Name | Value | Type | |||

|

| |||||

|

|

|

|

|

| |

| Number of IDELAY | C_NUM_ |

|

| ||

G50 | controllers instantiated. | 2 | integer | |||

IDELAYCTRL | ||||||

| Ignored it not |

|

| |||

|

|

|

|

| ||

|

|

|

|

|

| |

| Includes IDELAY |

| 1=Include IDELAY |

|

| |

|

| primitive |

|

| ||

G51 | primitive on GNT_N. | C_INCLUDE_ | 0 | integer | ||

| ||||||

Set by | GNT_DELAY | |||||

|

|

| ||||

| ignored if not |

| 0=No IDELAY primitive |

|

| |

|

|

|

|

| ||

|

|

|

|

|

| |

| Provides a means for |

|

|

|

| |

| BSB to pass LOC |

|

|

|

| |

| coordinates for |

|

|

|

| |

| IDELAYCTRLs for a |

| See Device |

|

| |

| given board to | C_IDELAY | Implementation section, |

|

| |

G52 | EDK and is optional for | subsection | NOT SET | string | ||

CTRL_LOC | ||||||

| user to set LOC | Support for allowed |

|

| ||

|

|

|

| |||

| constraints. This |

| values |

|

| |

| parameter has no |

|

|

|

| |

| impact on bridge |

|

|

|

| |

| functionality. |

|

|

|

| |

|

|

|

|

|

| |

|

| v3.0 Core Parameters Group |

|

| ||

|

|

|

|

|

| |

| PCI Configuration |

|

|

| std_logic_ | |

G53 | Space Header Device | C_DEVICE_ID | 0x0000 | |||

vector | ||||||

| ID |

|

|

| ||

|

|

|

|

| ||

|

|

|

|

|

| |

| PCI Configuration | C VENDOR_ |

|

| std_logic_ | |

G54 | Space Header Vendor | 0x0000 | ||||

ID | vector | |||||

| ID |

|

| |||

|

|

|

|

| ||

|

|

|

|

|

| |

| PCI Configuration | C CLASS |

|

| std_logic_ | |

G55 | Space Header Class | 0x000000 | ||||

CODE | vector | |||||

| Code |

|

| |||

|

|

|

|

| ||

|

|

|

|

|

| |

G56 | PCI Configuration | C REV ID | 0x00 | std_logic_ | ||

Space Header Rev ID | vector | |||||

|

|

|

| |||

|

|

|

|

|

| |

| PCI Configuration | C SUB |

|

| std_logic_ | |

G57 | Space Header | 0x0000 | ||||

SYSTEM ID | vector | |||||

| Subsystem ID |

|

| |||

|

|

|

|

| ||

|

|

|

|

|

| |

| PCI Configuration | C SUBSYSTE |

|

| std_logic_ | |

G58 | Space Header | M VENDOR_ | 0x0000 | |||

vector | ||||||

| Subsystem Vendor ID | ID |

|

| ||

|

|

|

| |||

|

|

|

|

|

| |

| PCI Configuration |

|

|

| std_logic_ | |

G59 | Space Header | C MAX LAT | 0x0F | |||

vector | ||||||

| Maximum Latency |

|

|

| ||

|

|

|

|

| ||

|

|

|

|

|

| |

| PCI Configuration |

|

|

| std_logic_ | |

G60 | Space Header | C_MIN_GNT | 0x04 | |||

vector | ||||||

| Minimum Grant |

|

|

| ||

|

|

|

|

| ||

|

|

|

|

|

| |

|

| Configuration |

|

| ||

|

|

|

|

|

| |

12 | www.xilinx.com | DS508 March 21, 2006 |

|

| Product Specification |