PLB PCI Full Bridge (v1.00a)

Writing 0xFEDC0000 to IPIFBAR2PCIBAR_1

Writing 0x40000000 to IPIFBAR2PCIBAR_2

Writing 0x12345680 to IPIFBAR2PCIBAR_3

Host Bridge Device Number Register Description

The Host Bridge Device Number register is included by setting C_INCLUDE_DEVNUM_REG=1. The register can be included only if configuration functionality is included (i.e., C_INCLUDE_PCI_CONFIG=1).

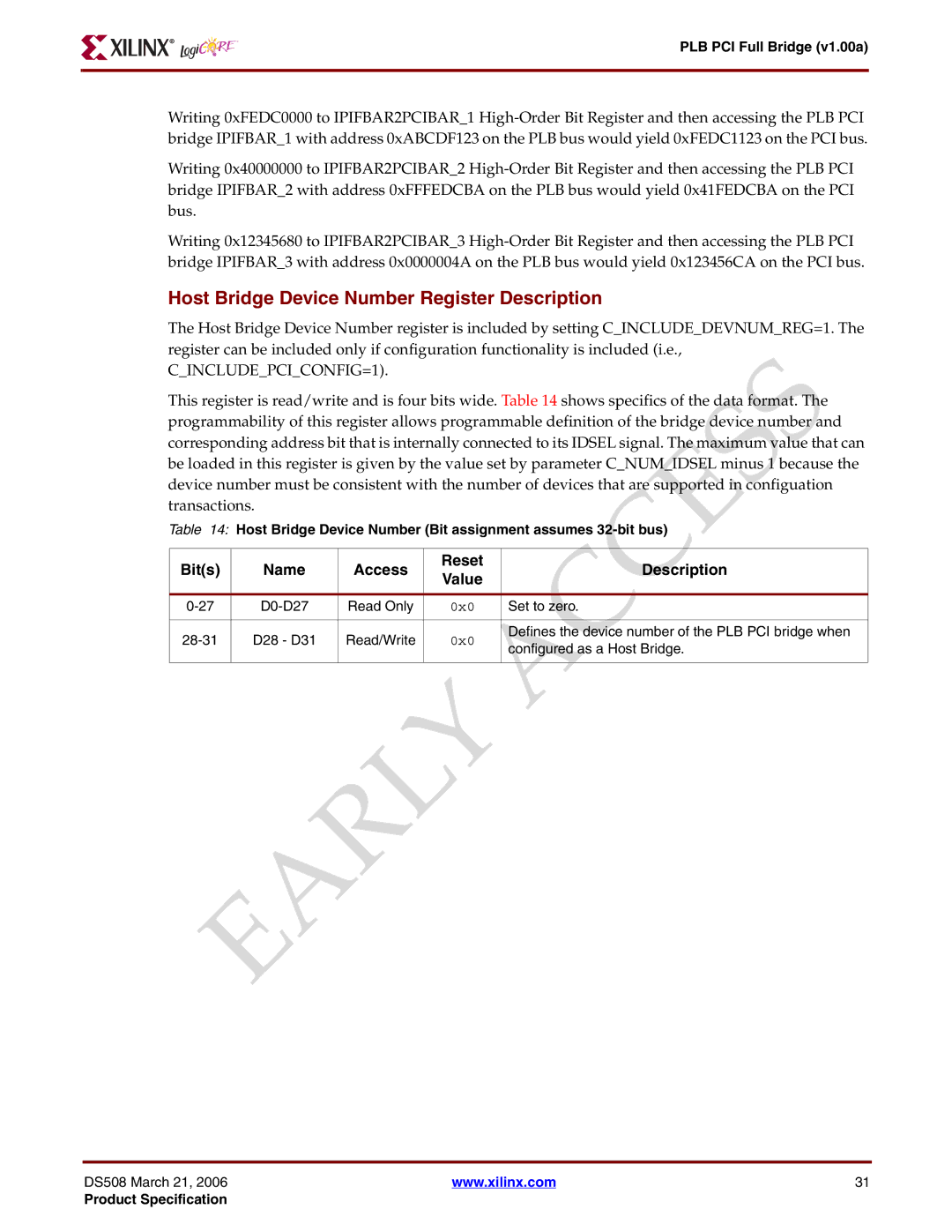

This register is read/write and is four bits wide. Table 14 shows specifics of the data format. The programmability of this register allows programmable definition of the bridge device number and corresponding address bit that is internally connected to its IDSEL signal. The maximum value that can be loaded in this register is given by the value set by parameter C NUM IDSEL minus 1 because the device number must be consistent with the number of devices that are supported in configuation transactions.

Table 14: Host Bridge Device Number (Bit assignment assumes 32-bit bus)

Bit(s) | Name | Access | Reset | Description | |

Value | |||||

|

|

|

| ||

|

|

|

|

| |

Read Only | 0x0 | Set to zero. | |||

|

|

|

|

| |

D28 - D31 | Read/Write | 0x0 | Defines the device number of the PLB PCI bridge when | ||

configured as a Host Bridge. | |||||

|

|

|

| ||

|

|

|

|

|

DS508 March 21, 2006 | www.xilinx.com | 31 |

Product Specification