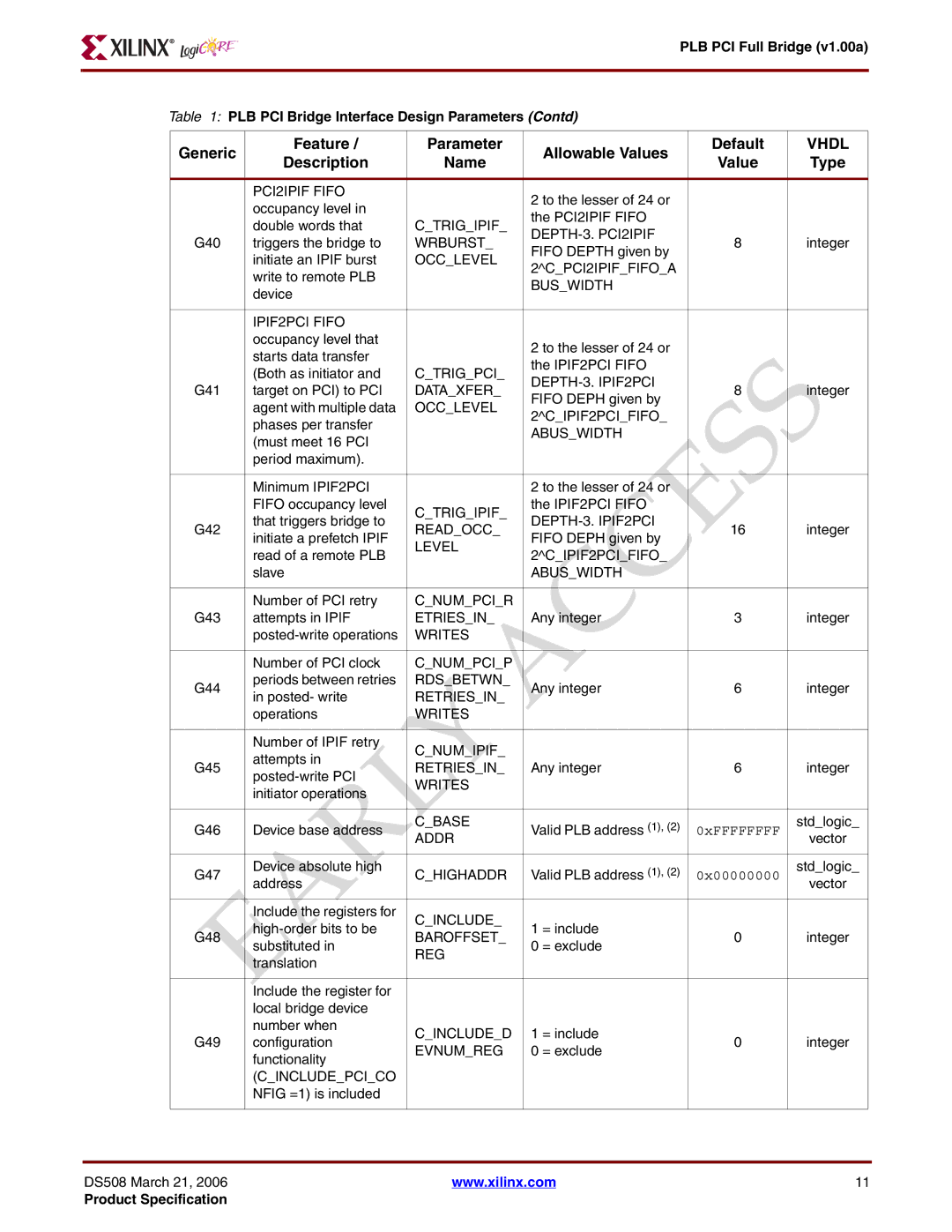

PLB PCI Full Bridge (v1.00a)

Table 1: PLB PCI Bridge Interface Design Parameters (Contd)

Generic | Feature / | Parameter | Allowable Values | Default | VHDL | |

Description | Name | Value | Type | |||

|

| |||||

|

|

|

|

|

| |

| PCI2IPIF FIFO |

| 2 to the lesser of 24 or |

|

| |

| occupancy level in |

|

|

| ||

|

| the PCI2IPIF FIFO |

|

| ||

| double words that | C_TRIG_IPIF_ |

|

| ||

|

|

|

| |||

G40 | triggers the bridge to | WRBURST_ | 8 | integer | ||

FIFO DEPTH given by | ||||||

| initiate an IPIF burst | OCC_LEVEL |

|

| ||

| 2^C_PCI2IPIF_FIFO_A |

|

| |||

| write to remote PLB |

|

|

| ||

|

| BUS_WIDTH |

|

| ||

| device |

|

|

| ||

|

|

|

|

| ||

|

|

|

|

|

| |

| IPIF2PCI FIFO |

|

|

|

| |

| occupancy level that |

| 2 to the lesser of 24 or |

|

| |

| starts data transfer |

|

|

| ||

|

| the IPIF2PCI FIFO |

|

| ||

| (Both as initiator and | C_TRIG_PCI_ |

|

| ||

|

|

|

| |||

G41 | target on PCI) to PCI | DATA_XFER_ | 8 | integer | ||

FIFO DEPH given by | ||||||

| agent with multiple data | OCC_LEVEL |

|

| ||

| 2^C IPIF2PCI FIFO |

|

| |||

| phases per transfer |

|

|

| ||

|

| ABUS WIDTH |

|

| ||

| (must meet 16 PCI |

|

|

| ||

|

|

|

|

| ||

| period maximum). |

|

|

|

| |

|

|

|

|

|

| |

| Minimum IPIF2PCI |

| 2 to the lesser of 24 or |

|

| |

| FIFO occupancy level | C_TRIG_IPIF | the IPIF2PCI FIFO |

|

| |

| that triggers bridge to |

|

| |||

G42 | READ_OCC_ | 16 | integer | |||

initiate a prefetch IPIF | FIFO DEPH given by | |||||

| LEVEL |

|

| |||

| read of a remote PLB | 2^C IPIF2PCI FIFO |

|

| ||

|

|

|

| |||

| slave |

| ABUS WIDTH |

|

| |

|

|

|

|

|

| |

| Number of PCI retry | C_NUM_PCI R |

|

|

| |

G43 | attempts in IPIF | ETRIES_IN_ | Any integer | 3 | integer | |

| WRITES |

|

|

| ||

|

|

|

|

|

| |

| Number of PCI clock | C_NUM_PCI P |

|

|

| |

G44 | periods between retries | RDS_BETWN | Any integer | 6 | integer | |

in posted- write | RETRIES_IN | |||||

|

|

|

| |||

| operations | WRITES |

|

|

| |

|

|

|

|

|

| |

| Number of IPIF retry | C NUM IPIF_ |

|

|

| |

| attempts in |

|

|

| ||

G45 | RETRIES_IN_ | Any integer | 6 | integer | ||

| WRITES |

|

|

| ||

| initiator operations |

|

|

| ||

|

|

|

|

| ||

|

|

|

|

|

| |

G46 | Device base address | C BASE | Valid PLB address (1), (2) | 0xFFFFFFFF | std_logic_ | |

|

| ADDR |

|

| vector | |

|

|

|

|

|

| |

G47 | Device absolute high | C_HIGHADDR | Valid PLB address (1), (2) | 0x00000000 | std_logic_ | |

| address |

|

|

| vector | |

|

|

|

|

|

| |

| Include the registers for | C_INCLUDE_ |

|

|

| |

| 1 = include |

|

| |||

G48 | BAROFFSET_ | 0 | integer | |||

substituted in | 0 = exclude | |||||

| REG |

|

| |||

| translation |

|

|

| ||

|

|

|

|

| ||

|

|

|

|

|

| |

| Include the register for |

|

|

|

| |

| local bridge device |

|

|

|

| |

| number when | C_INCLUDE_D | 1 = include |

|

| |

G49 | configuration | 0 | integer | |||

EVNUM_REG | 0 = exclude | |||||

| functionality |

|

| |||

|

|

|

|

| ||

| (C_INCLUDE_PCI_CO |

|

|

|

| |

| NFIG =1) is included |

|

|

|

| |

|

|

|

|

|

|

DS508 March 21, 2006 | www.xilinx.com | 11 |

Product Specification