PLB PCI Full Bridge (v1.00a)

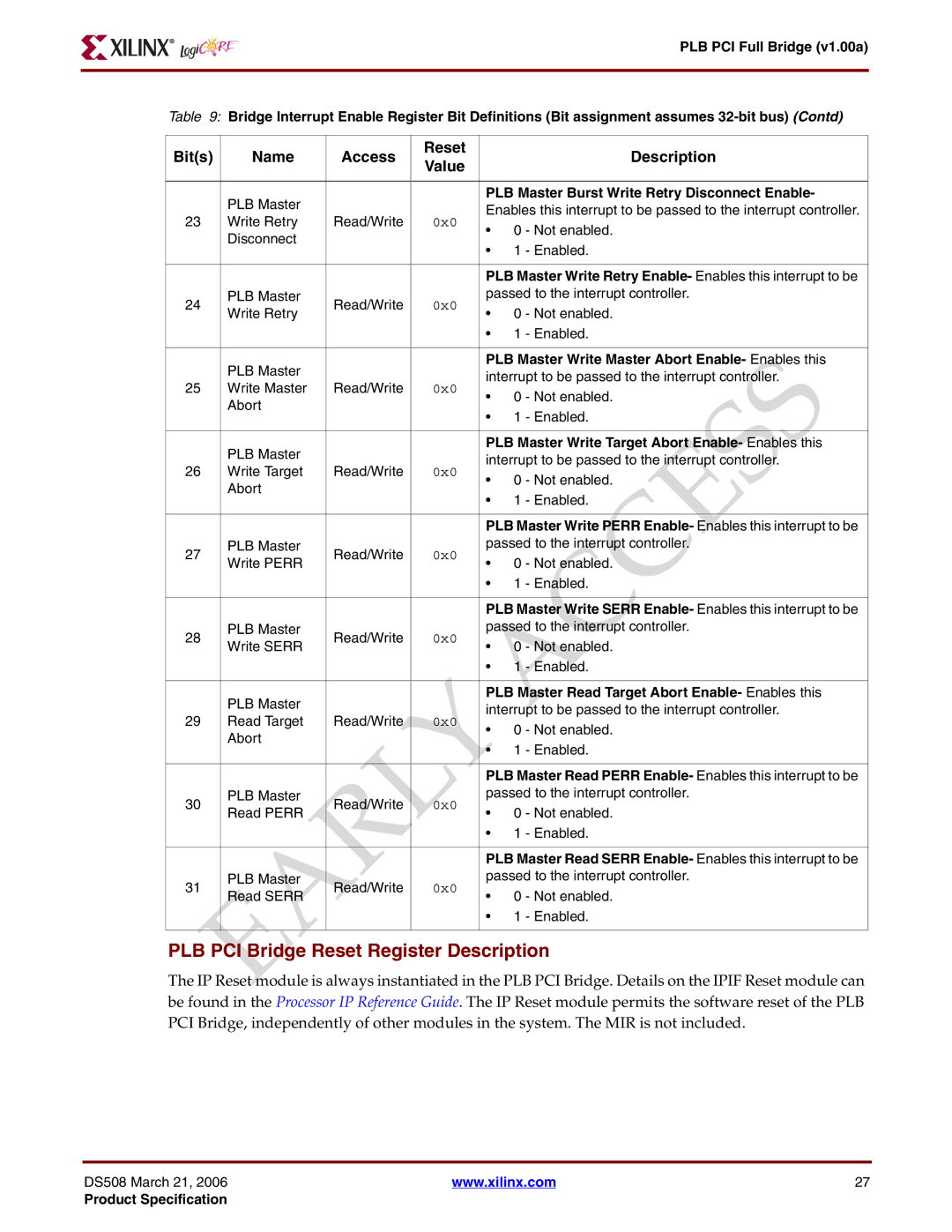

Table 9: Bridge Interrupt Enable Register Bit Definitions (Bit assignment assumes

Bit(s) | Name | Access | Reset |

|

| Description | |

Value |

|

| |||||

|

|

|

|

|

| ||

|

|

|

|

| |||

| PLB Master |

|

| PLB Master Burst Write Retry Disconnect Enable- | |||

|

|

| Enables this interrupt to be passed to the interrupt controller. | ||||

23 | Write Retry | Read/Write | 0x0 | ||||

• | 0 | - Not enabled. | |||||

| Disconnect |

|

| ||||

|

|

| • | 1 | - Enabled. | ||

|

|

|

| ||||

|

|

|

|

| |||

|

|

|

| PLB Master Write Retry Enable- Enables this interrupt to be | |||

24 | PLB Master | Read/Write | 0x0 | passed to the interrupt controller. | |||

Write Retry | • | 0 | - Not enabled. | ||||

|

|

| |||||

|

|

|

| • | 1 | - Enabled. | |

|

|

|

|

| |||

| PLB Master |

|

| PLB Master Write Master Abort Enable- Enables this | |||

|

|

| interrupt to be passed to the interrupt controller. | ||||

25 | Write Master | Read/Write | 0x0 | ||||

• | 0 | - Not enabled. | |||||

| Abort |

|

| ||||

|

|

| • | 1 | - Enabled. | ||

|

|

|

| ||||

|

|

|

|

| |||

| PLB Master |

|

| PLB Master Write Target Abort Enable- Enables this | |||

|

|

| interrupt to be passed to the interrupt controller. | ||||

26 | Write Target | Read/Write | 0x0 | ||||

• | 0 | - Not enabled. | |||||

| Abort |

|

| ||||

|

|

| • | 1 | - Enabled. | ||

|

|

|

| ||||

|

|

|

|

| |||

|

|

|

| PLB Master Write PERR Enable- Enables this interrupt to be | |||

27 | PLB Master | Read/Write | 0x0 | passed to the interrupt controller. | |||

Write PERR | • | 0 | - Not enabled. | ||||

|

|

| |||||

|

|

|

| • | 1 | - Enabled. | |

|

|

|

|

| |||

|

|

|

| PLB Master Write SERR Enable- Enables this interrupt to be | |||

28 | PLB Master | Read/Write | 0x0 | passed to the interrupt controller. | |||

Write SERR | • | 0 | - Not enabled. | ||||

|

|

| |||||

|

|

|

| • | 1 | - Enabled. | |

|

|

|

|

| |||

| PLB Master |

|

| PLB Master Read Target Abort Enable- Enables this | |||

|

|

| interrupt to be passed to the interrupt controller. | ||||

29 | Read Target | Read/Write | 0x0 | ||||

• | 0 | - Not enabled. | |||||

| Abort |

|

| ||||

|

|

| • | 1 | - Enabled. | ||

|

|

|

| ||||

|

|

|

|

| |||

|

|

|

| PLB Master Read PERR Enable- Enables this interrupt to be | |||

30 | PLB Master | Read/Write | 0x0 | passed to the interrupt controller. | |||

Read PERR | • | 0 | - Not enabled. | ||||

|

|

| |||||

|

|

|

| • | 1 | - Enabled. | |

|

|

|

|

| |||

|

|

|

| PLB Master Read SERR Enable- Enables this interrupt to be | |||

31 | PLB Master | Read/Write | 0x0 | passed to the interrupt controller. | |||

Read SERR | • | 0 | - Not enabled. | ||||

|

|

| |||||

|

|

|

| • | 1 | - Enabled. | |

|

|

|

|

|

|

| |

PLB PCI Bridge Reset Register Description

The IP Reset module is always instantiated in the PLB PCI Bridge. Details on the IPIF Reset module can be found in the Processor IP Reference Guide. The IP Reset module permits the software reset of the PLB PCI Bridge, independently of other modules in the system. The MIR is not included.

DS508 March 21, 2006 | www.xilinx.com | 27 |

Product Specification