PLB PCI Full Bridge (v1.00a)

Design Debug

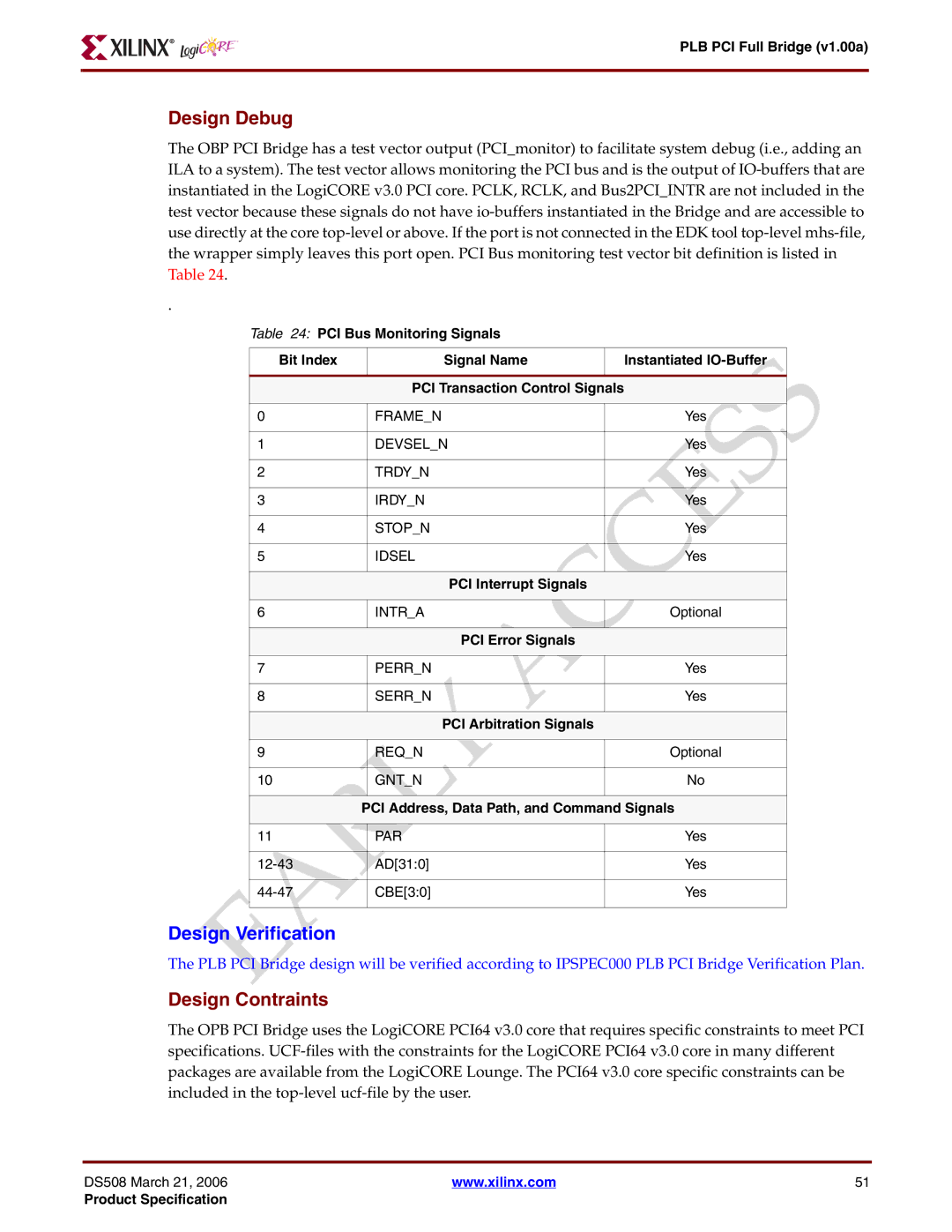

The OBP PCI Bridge has a test vector output (PCI_monitor) to facilitate system debug (i.e., adding an ILA to a system). The test vector allows monitoring the PCI bus and is the output of

.

Table 24: PCI Bus Monitoring Signals

Bit Index |

| Signal Name |

| Instantiated |

|

|

|

|

|

|

| PCI Transaction Control Signals |

| |

|

|

|

|

|

0 |

| FRAME_N |

| Yes |

|

|

|

|

|

1 |

| DEVSEL_N |

| Yes |

|

|

|

|

|

2 |

| TRDY_N |

| Yes |

|

|

|

|

|

3 |

| IRDY_N |

| Yes |

|

|

|

|

|

4 |

| STOP_N |

| Yes |

|

|

|

|

|

5 |

| IDSEL |

| Yes |

|

|

|

|

|

|

| PCI Interrupt Signals |

| |

|

|

|

|

|

6 |

| INTR_A |

| Optional |

|

|

|

|

|

|

| PCI Error Signals |

| |

|

|

|

|

|

7 |

| PERR_N |

| Yes |

|

|

|

|

|

8 |

| SERR_N |

| Yes |

|

|

|

|

|

|

| PCI Arbitration Signals |

| |

|

|

|

|

|

9 |

| REQ N |

| Optional |

|

|

|

|

|

10 |

| GNT N |

| No |

|

|

|

| |

| PCI Address, Data Path, and Command Signals | |||

|

|

|

|

|

11 |

| PAR |

| Yes |

|

|

|

|

|

| AD[31:0] |

| Yes | |

|

|

|

|

|

| CBE[3:0] |

| Yes | |

|

|

|

|

|

Design Verification

The PLB PCI Bridge design will be verified according to IPSPEC000 PLB PCI Bridge Verification Plan.

Design Contraints

The OPB PCI Bridge uses the LogiCORE PCI64 v3.0 core that requires specific constraints to meet PCI specifications.

DS508 March 21, 2006 | www.xilinx.com | 51 |

Product Specification