PLB PCI Full Bridge (v1.00a)

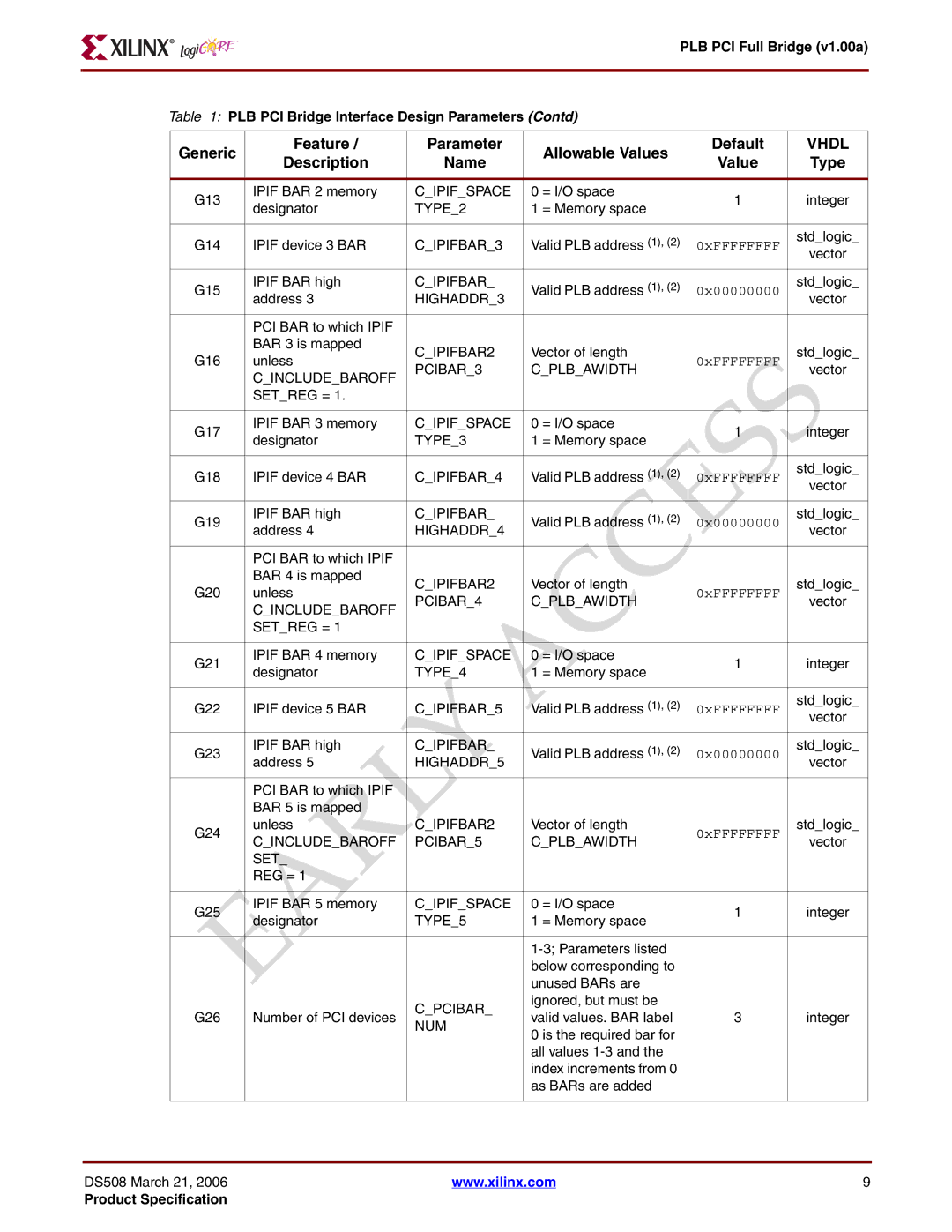

Table 1: PLB PCI Bridge Interface Design Parameters (Contd)

Generic | Feature / | Parameter | Allowable Values | Default | VHDL | |

Description | Name | Value | Type | |||

|

| |||||

|

|

|

|

|

| |

G13 | IPIF BAR 2 memory | C_IPIF_SPACE | 0 = I/O space | 1 | integer | |

designator | TYPE_2 | 1 = Memory space | ||||

|

|

| ||||

|

|

|

|

|

| |

G14 | IPIF device 3 BAR | C_IPIFBAR_3 | Valid PLB address (1), (2) | 0xFFFFFFFF | std_logic_ | |

|

|

|

|

| vector | |

|

|

|

|

|

| |

G15 | IPIF BAR high | C_IPIFBAR_ | Valid PLB address (1), (2) | 0x00000000 | std_logic_ | |

| address 3 | HIGHADDR_3 |

|

| vector | |

|

|

|

|

|

| |

| PCI BAR to which IPIF |

|

|

|

| |

| BAR 3 is mapped | C_IPIFBAR2 | Vector of length |

| std_logic_ | |

G16 | unless | 0xFFFFFFFF | ||||

| C_INCLUDE_BAROFF | PCIBAR_3 | C_PLB_AWIDTH |

| vector | |

|

|

|

|

| ||

| SET_REG = 1. |

|

|

|

| |

|

|

|

|

|

| |

G17 | IPIF BAR 3 memory | C_IPIF_SPACE | 0 = I/O space | 1 | integer | |

designator | TYPE_3 | 1 = Memory space | ||||

|

|

| ||||

|

|

|

|

|

| |

G18 | IPIF device 4 BAR | C_IPIFBAR_4 | Valid PLB address (1), (2) | 0xFFFFFFFF | std_logic_ | |

|

|

|

|

| vector | |

|

|

|

|

|

| |

G19 | IPIF BAR high | C_IPIFBAR_ | Valid PLB address (1), (2) | 0x00000000 | std_logic_ | |

| address 4 | HIGHADDR_4 |

|

| vector | |

|

|

|

|

|

| |

| PCI BAR to which IPIF |

|

|

|

| |

| BAR 4 is mapped | C_IPIFBAR2 | Vector of length |

| std_logic_ | |

G20 | unless | 0xFFFFFFFF | ||||

| C_INCLUDE_BAROFF | PCIBAR_4 | C PLB AWIDTH |

| vector | |

|

|

|

|

| ||

| SET_REG = 1 |

|

|

|

| |

|

|

|

|

|

| |

G21 | IPIF BAR 4 memory | C_IPIF_SPACE | 0 = I/O space | 1 | integer | |

designator | TYPE_4 | 1 = Memory space | ||||

|

|

| ||||

|

|

|

|

|

| |

G22 | IPIF device 5 BAR | C IPIFBAR_5 | Valid PLB address (1), (2) | 0xFFFFFFFF | std_logic_ | |

|

|

|

|

| vector | |

|

|

|

|

|

| |

G23 | IPIF BAR high | C IPIFBAR_ | Valid PLB address (1), (2) | 0x00000000 | std_logic_ | |

| address 5 | HIGHADDR_5 |

|

| vector | |

|

|

|

|

|

| |

| PCI BAR to which IPIF |

|

|

|

| |

| BAR 5 is mapped |

|

|

|

| |

G24 | unless | C IPIFBAR2 | Vector of length | 0xFFFFFFFF | std_logic_ | |

| C_INCLUDE BAROFF | PCIBAR_5 | C_PLB_AWIDTH |

| vector | |

| SET |

|

|

|

| |

| REG = 1 |

|

|

|

| |

|

|

|

|

|

| |

G25 | IPIF BAR 5 memory | C_IPIF_SPACE | 0 = I/O space | 1 | integer | |

designator | TYPE_5 | 1 = Memory space | ||||

|

|

| ||||

|

|

|

|

|

| |

|

|

|

|

| ||

|

|

| below corresponding to |

|

| |

|

|

| unused BARs are |

|

| |

|

| C_PCIBAR_ | ignored, but must be |

|

| |

G26 | Number of PCI devices | valid values. BAR label | 3 | integer | ||

NUM | ||||||

|

| 0 is the required bar for |

|

| ||

|

|

|

|

| ||

|

|

| all values |

|

| |

|

|

| index increments from 0 |

|

| |

|

|

| as BARs are added |

|

| |

|

|

|

|

|

|

DS508 March 21, 2006 | www.xilinx.com | 9 |

Product Specification