PLB PCI Full Bridge (v1.00a)

bus number. The highest subordinate bus number is also an

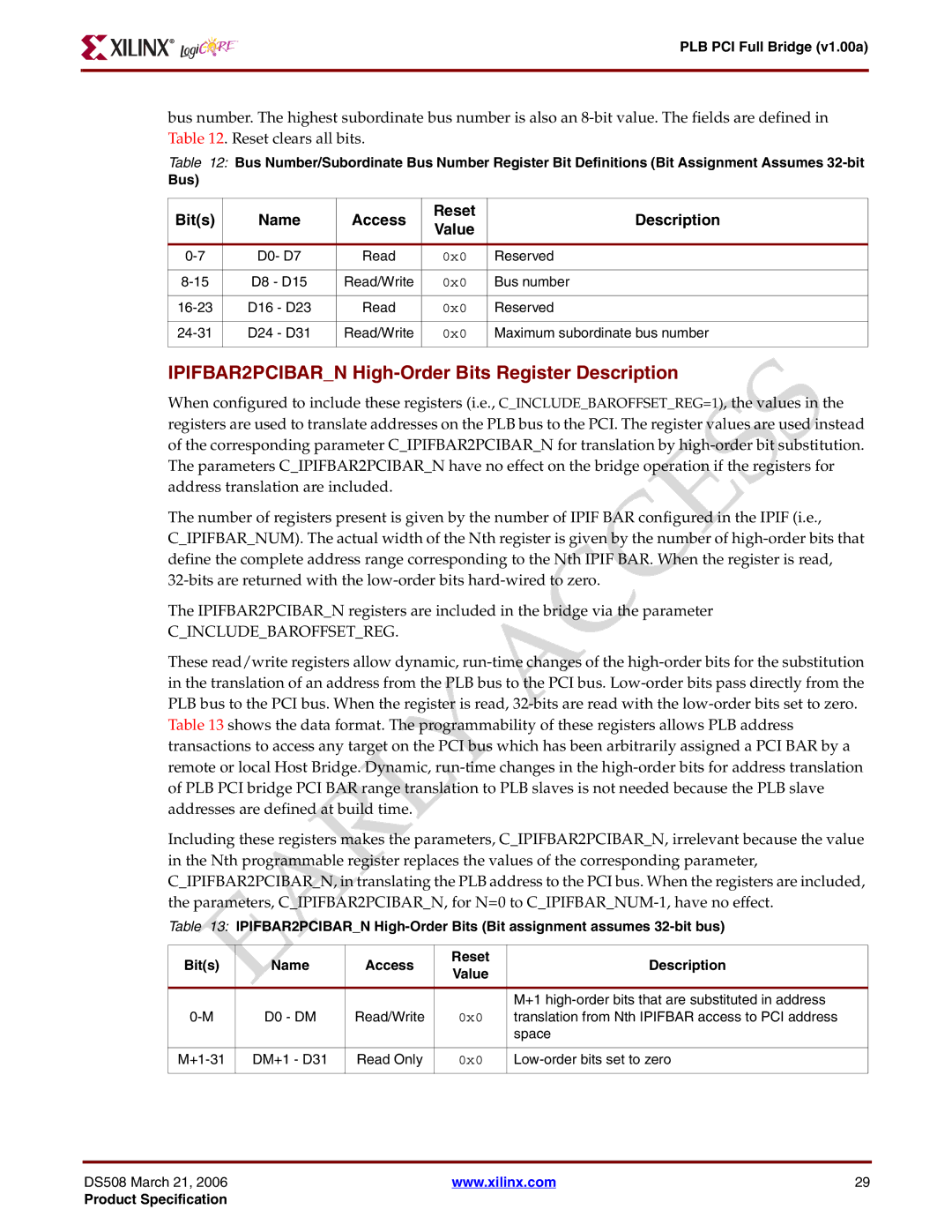

Table 12: Bus Number/Subordinate Bus Number Register Bit Definitions (Bit Assignment Assumes

Bus)

Bit(s) | Name | Access | Reset | Description | |

Value | |||||

|

|

|

| ||

|

|

|

|

| |

D0- D7 | Read | 0x0 | Reserved | ||

|

|

|

|

| |

D8 - D15 | Read/Write | 0x0 | Bus number | ||

|

|

|

|

| |

D16 - D23 | Read | 0x0 | Reserved | ||

|

|

|

|

| |

D24 - D31 | Read/Write | 0x0 | Maximum subordinate bus number | ||

|

|

|

|

|

IPIFBAR2PCIBAR_N High-Order Bits Register Description

When configured to include these registers (i.e., C INCLUDE BAROFFSET REG=1), the values in the registers are used to translate addresses on the PLB bus to the PCI. The register values are used instead of the corresponding parameter C_IPIFBAR2PCIBAR N for translation by

The number of registers present is given by the number of IPIF BAR configured in the IPIF (i.e.,

C_IPIFBAR_NUM). The actual width of the Nth register is given by the number of

The IPIFBAR2PCIBAR_N registers are included in the bridge via the parameter

C_INCLUDE_BAROFFSET_REG.

These read/write registers allow dynamic,

Including these registers makes the parameters, C_IPIFBAR2PCIBAR_N, irrelevant because the value in the Nth programmable register replaces the values of the corresponding parameter, C_IPIFBAR2PCIBAR N, in translating the PLB address to the PCI bus. When the registers are included, the parameters, C IPIFBAR2PCIBAR_N, for N=0 to

Table 13: IPIFBAR2PCIBAR N

Bit(s) | Name | Access | Reset | Description | |

Value | |||||

|

|

|

| ||

|

|

|

|

| |

|

|

|

| M+1 | |

D0 - DM | Read/Write | 0x0 | translation from Nth IPIFBAR access to PCI address | ||

|

|

|

| space | |

|

|

|

|

| |

DM+1 - D31 | Read Only | 0x0 | |||

|

|

|

|

|

DS508 March 21, 2006 | www.xilinx.com | 29 |

Product Specification