|

|

|

|

|

|

| Ref.: |

|

| |

|

|

|

| SpaceWire Router |

| UserManual |

| |||

|

|

|

| Issue: | 3.4 |

|

| |||

|

|

|

|

|

| User Manual |

|

| ||

|

|

|

|

|

| Date: | 11th July 2008 |

| ||

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| |||

|

|

| Table |

|

|

| ||||

|

|

|

|

|

|

|

|

| ||

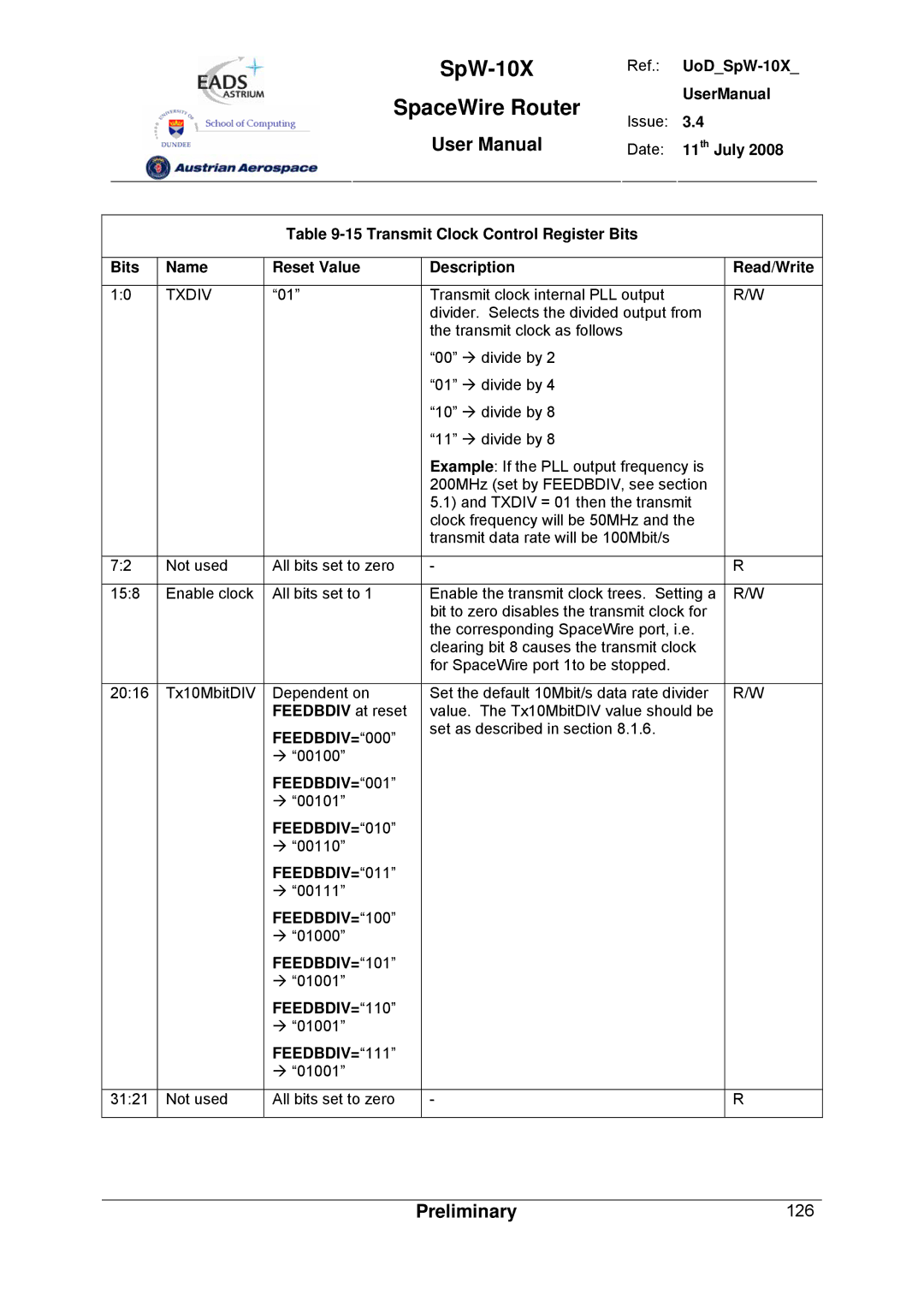

Bits | Name | Reset Value |

| Description |

|

| Read/Write |

| ||

|

|

|

|

|

|

|

| |||

1:0 | TXDIV | “01” |

| Transmit clock internal PLL output |

| R/W |

| |||

|

|

|

|

|

| divider. Selects the divided output from |

|

| ||

|

|

|

|

|

| the transmit clock as follows |

|

|

|

|

|

|

|

|

|

| “00” Æ divide by 2 |

|

|

|

|

|

|

|

|

|

| “01” Æ divide by 4 |

|

|

|

|

|

|

|

|

|

| “10” Æ divide by 8 |

|

|

|

|

|

|

|

|

|

| “11” Æ divide by 8 |

|

|

|

|

|

|

|

|

|

| Example: If the PLL output frequency is |

|

| ||

|

|

|

|

|

| 200MHz (set by FEEDBDIV, see section |

|

| ||

|

|

|

|

|

| 5.1) and TXDIV = 01 then the transmit |

|

| ||

|

|

|

|

|

| clock frequency will be 50MHz and the |

|

| ||

|

|

|

|

|

| transmit data rate will be 100Mbit/s |

|

|

| |

|

|

|

|

|

|

|

|

| ||

7:2 | Not used | All bits set to zero |

| - |

|

| R |

| ||

|

|

|

|

|

|

| ||||

15:8 | Enable clock | All bits set to 1 |

| Enable the transmit clock trees. Setting a | R/W |

| ||||

|

|

|

|

|

| bit to zero disables the transmit clock for |

|

| ||

|

|

|

|

|

| the corresponding SpaceWire port, i.e. |

|

| ||

|

|

|

|

|

| clearing bit 8 causes the transmit clock |

|

| ||

|

|

|

|

|

| for SpaceWire port 1to be stopped. |

|

|

| |

|

|

|

|

|

|

| ||||

20:16 | Tx10MbitDIV | Dependent on |

| Set the default 10Mbit/s data rate divider | R/W |

| ||||

|

|

| FEEDBDIV at reset |

| value. The Tx10MbitDIV value should be |

|

| |||

|

|

| FEEDBDIV=“000” |

| set as described in section 8.1.6. |

|

|

| ||

|

|

|

|

|

|

|

|

| ||

|

|

| Æ “00100” |

|

|

|

|

|

| |

|

|

| FEEDBDIV=“001” |

|

|

|

|

|

| |

|

|

| Æ “00101” |

|

|

|

|

|

| |

|

|

| FEEDBDIV=“010” |

|

|

|

|

|

| |

|

|

| Æ “00110” |

|

|

|

|

|

| |

|

|

| FEEDBDIV=“011” |

|

|

|

|

|

| |

|

|

| Æ “00111” |

|

|

|

|

|

| |

|

|

| FEEDBDIV=“100” |

|

|

|

|

|

| |

|

|

| Æ “01000” |

|

|

|

|

|

| |

|

|

| FEEDBDIV=“101” |

|

|

|

|

|

| |

|

|

| Æ “01001” |

|

|

|

|

|

| |

|

|

| FEEDBDIV=“110” |

|

|

|

|

|

| |

|

|

| Æ “01001” |

|

|

|

|

|

| |

|

|

| FEEDBDIV=“111” |

|

|

|

|

|

| |

|

|

| Æ “01001” |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| ||

31:21 | Not used | All bits set to zero |

| - |

|

| R |

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Preliminary |

|

| 126 |

| |