| Ref.: |

| |

SpaceWire Router |

| UserManual | |

Issue: | 3.4 | ||

User Manual | |||

Date: | 11th July 2008 | ||

|

|

|

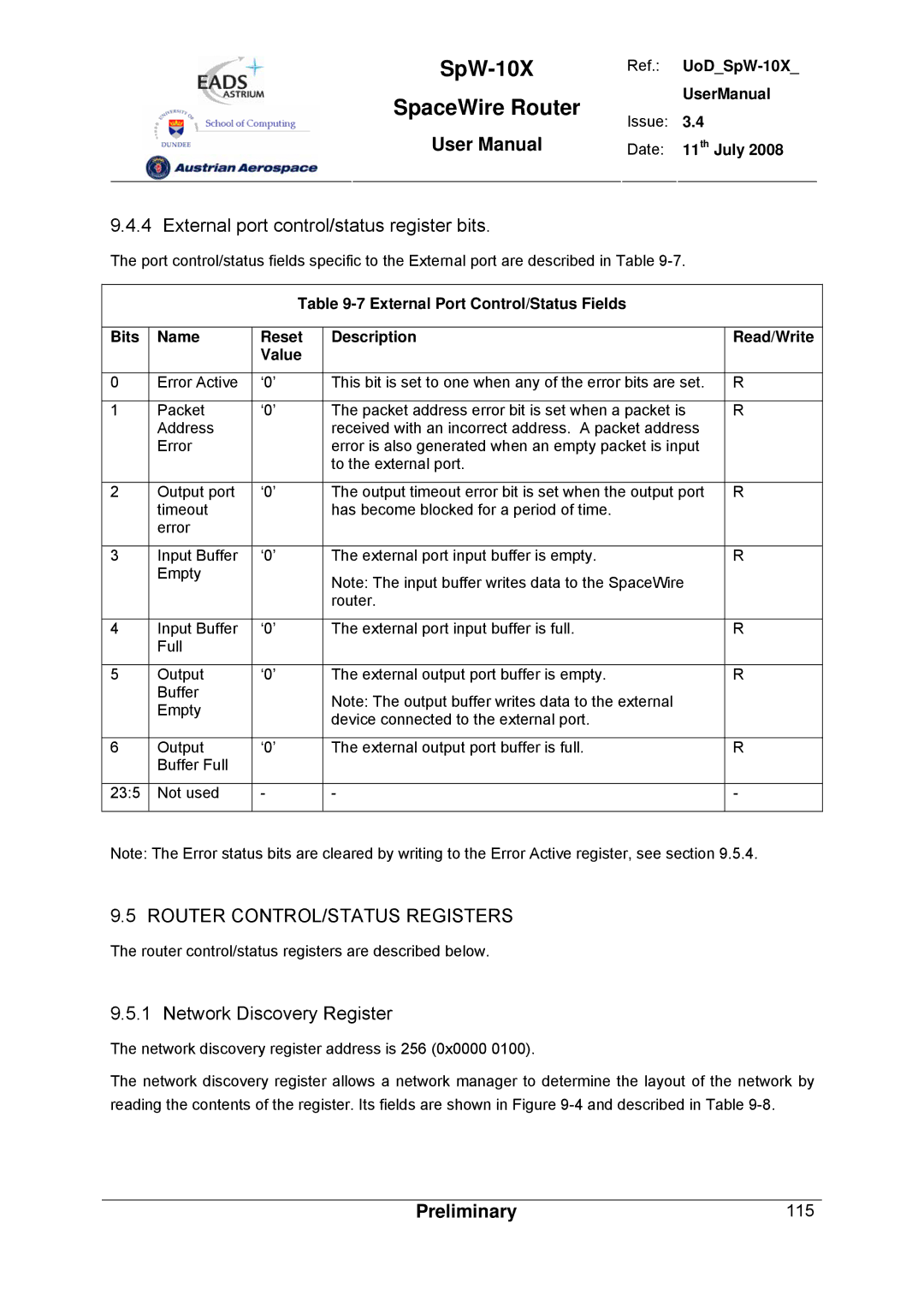

9.4.4 External port control/status register bits.

The port control/status fields specific to the External port are described in Table

Table

Bits | Name | Reset | Description | Read/Write |

|

| Value |

|

|

|

|

|

|

|

0 | Error Active | ‘0’ | This bit is set to one when any of the error bits are set. | R |

|

|

|

|

|

1 | Packet | ‘0’ | The packet address error bit is set when a packet is | R |

| Address |

| received with an incorrect address. A packet address |

|

| Error |

| error is also generated when an empty packet is input |

|

|

|

| to the external port. |

|

|

|

|

|

|

2 | Output port | ‘0’ | The output timeout error bit is set when the output port | R |

| timeout |

| has become blocked for a period of time. |

|

| error |

|

|

|

|

|

|

|

|

3 | Input Buffer | ‘0’ | The external port input buffer is empty. | R |

| Empty |

| Note: The input buffer writes data to the SpaceWire |

|

|

|

|

| |

|

|

| router. |

|

|

|

|

|

|

4 | Input Buffer | ‘0’ | The external port input buffer is full. | R |

| Full |

|

|

|

|

|

|

|

|

5 | Output | ‘0’ | The external output port buffer is empty. | R |

| Buffer |

| Note: The output buffer writes data to the external |

|

| Empty |

|

| |

|

| device connected to the external port. |

| |

|

|

|

| |

|

|

|

|

|

6 | Output | ‘0’ | The external output port buffer is full. | R |

| Buffer Full |

|

|

|

|

|

|

|

|

23:5 | Not used | - | - | - |

|

|

|

|

|

Note: The Error status bits are cleared by writing to the Error Active register, see section 9.5.4.

9.5 ROUTER CONTROL/STATUS REGISTERS

The router control/status registers are described below.

9.5.1 Network Discovery Register

The network discovery register address is 256 (0x0000 0100).

The network discovery register allows a network manager to determine the layout of the network by reading the contents of the register. Its fields are shown in Figure

Preliminary | 115 |