| Ref.: |

| |

SpaceWire Router |

| UserManual | |

Issue: | 3.4 | ||

User Manual | |||

Date: | 11th July 2008 | ||

|

|

|

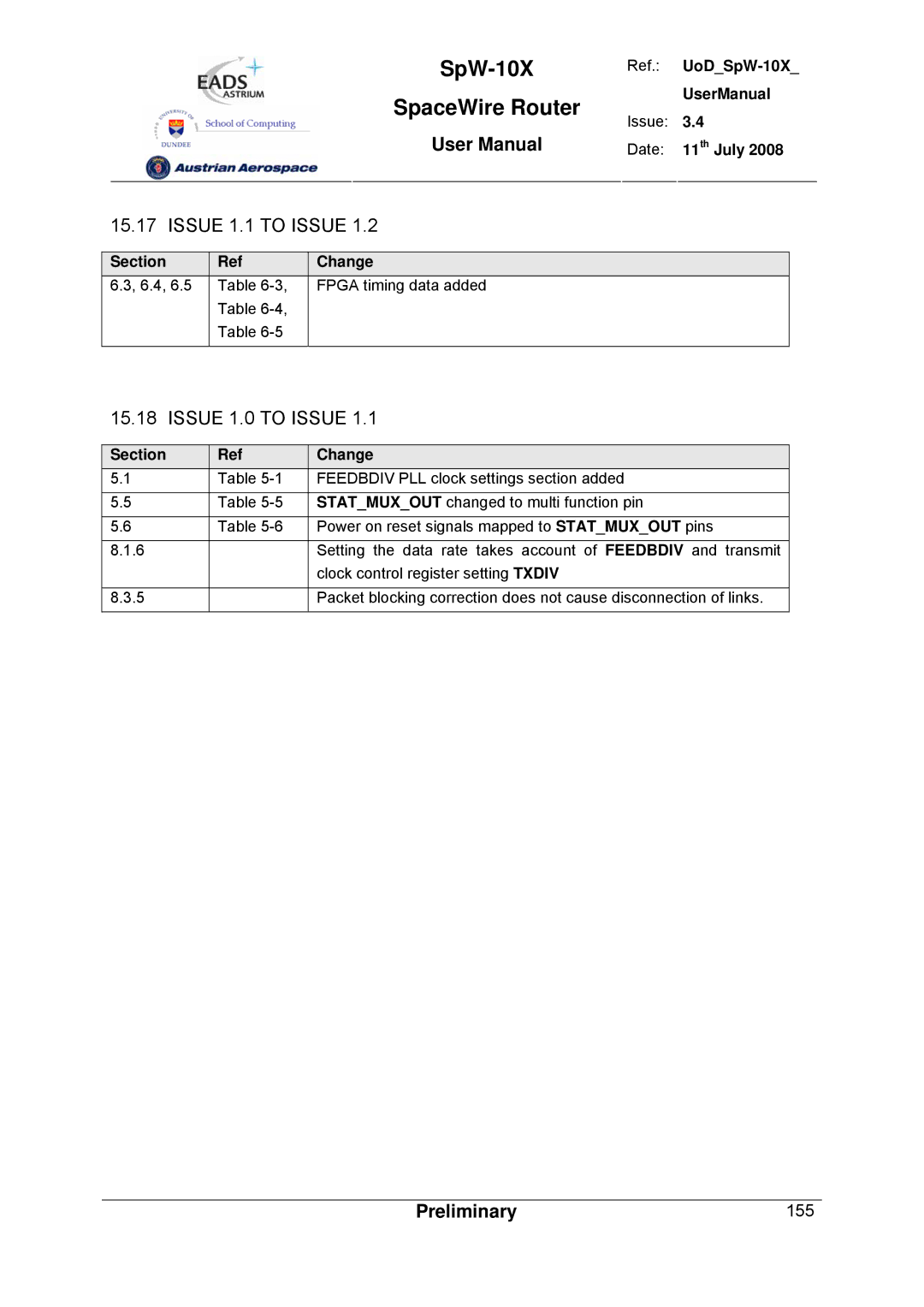

15.17 ISSUE 1.1 TO ISSUE 1.2

Section | Ref | Change |

6.3, 6.4, 6.5 | Table | FPGA timing data added |

| Table |

|

| Table |

|

|

|

|

15.18 ISSUE 1.0 TO ISSUE 1.1

Section | Ref | Change |

5.1 | Table | FEEDBDIV PLL clock settings section added |

|

|

|

5.5 | Table | STAT_MUX_OUT changed to multi function pin |

|

|

|

5.6 | Table | Power on reset signals mapped to STAT_MUX_OUT pins |

8.1.6 |

| Setting the data rate takes account of FEEDBDIV and transmit |

|

| clock control register setting TXDIV |

|

|

|

8.3.5 |

| Packet blocking correction does not cause disconnection of links. |

|

|

|

Preliminary | 155 |