|

|

|

|

| Ref.: |

|

| |

|

|

| SpaceWire Router |

| UserManual |

| ||

|

|

| Issue: | 3.4 |

|

| ||

|

|

|

| User Manual |

|

| ||

|

|

|

| Date: | 11th July 2008 |

| ||

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| |

| Table |

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| Signal | Dir |

| Description |

|

| Signal |

|

|

|

|

|

|

|

| Type |

|

|

|

|

|

|

| |||

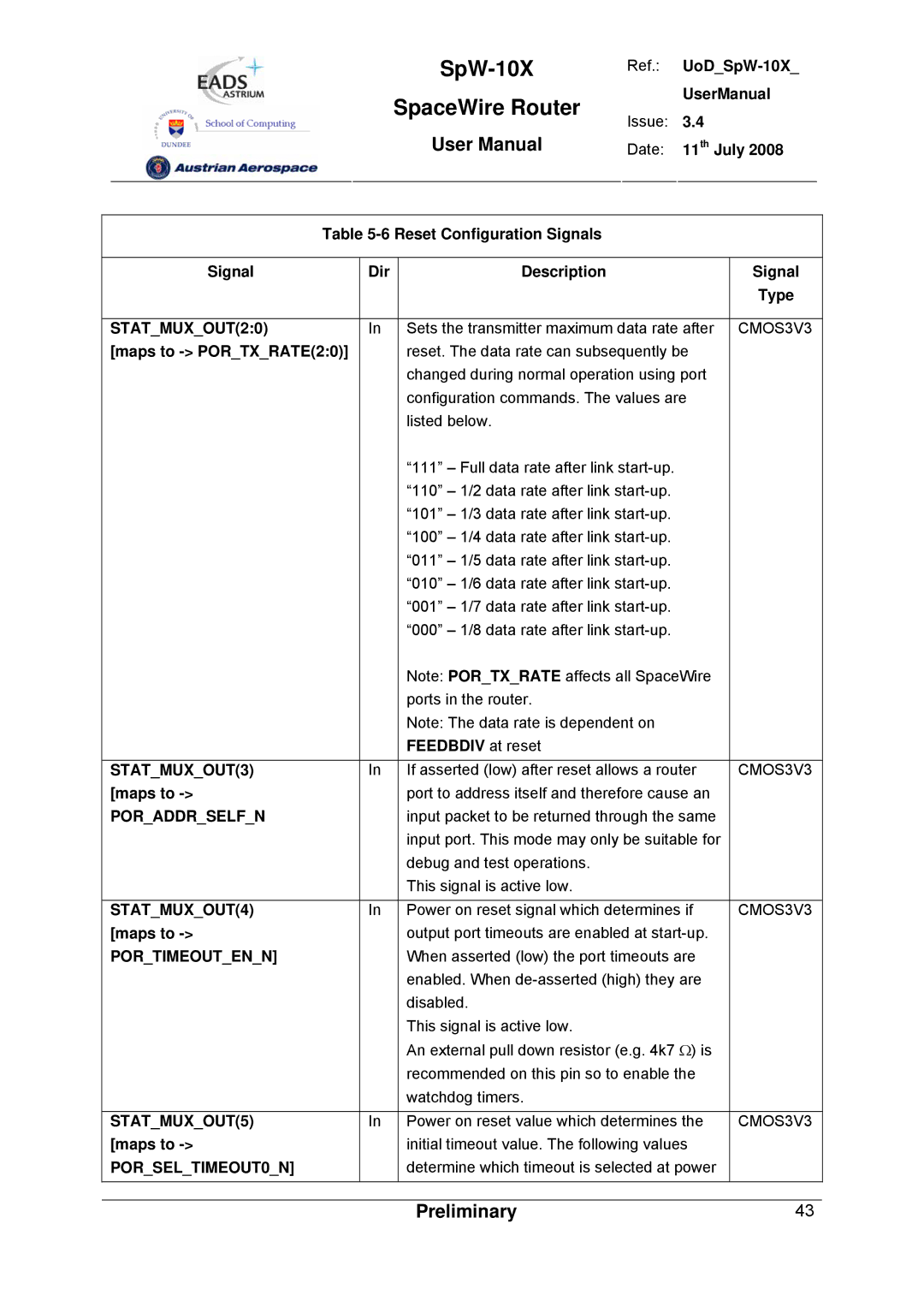

STAT_MUX_OUT(2:0) | In |

| Sets the transmitter maximum data rate after | CMOS3V3 |

| |||

[maps to |

|

| reset. The data rate can subsequently be |

|

| |||

|

|

|

| changed during normal operation using port |

|

| ||

|

|

|

| configuration commands. The values are |

|

| ||

|

|

|

| listed below. |

|

|

|

|

|

|

|

| “111” – Full data rate after link |

|

|

| |

|

|

|

| “110” – 1/2 data rate after link |

|

|

| |

|

|

|

| “101” – 1/3 data rate after link |

|

|

| |

|

|

|

| “100” – 1/4 data rate after link |

|

|

| |

|

|

|

| “011” – 1/5 data rate after link |

|

|

| |

|

|

|

| “010” – 1/6 data rate after link |

|

|

| |

|

|

|

| “001” – 1/7 data rate after link |

|

|

| |

|

|

|

| “000” – 1/8 data rate after link |

|

|

| |

|

|

|

| Note: POR_TX_RATE affects all SpaceWire |

|

| ||

|

|

|

| ports in the router. |

|

|

|

|

|

|

|

| Note: The data rate is dependent on |

|

|

| |

|

|

|

| FEEDBDIV at reset |

|

|

|

|

|

|

|

|

|

| |||

STAT_MUX_OUT(3) | In |

| If asserted (low) after reset allows a router | CMOS3V3 |

| |||

[maps to |

|

| port to address itself and therefore cause an |

|

| |||

POR_ADDR_SELF_N |

|

| input packet to be returned through the same |

|

| |||

|

|

|

| input port. This mode may only be suitable for |

|

| ||

|

|

|

| debug and test operations. |

|

|

|

|

|

|

|

| This signal is active low. |

|

|

|

|

|

|

|

|

|

| |||

STAT_MUX_OUT(4) | In |

| Power on reset signal which determines if | CMOS3V3 |

| |||

[maps to |

|

| output port timeouts are enabled at |

|

| |||

POR_TIMEOUT_EN_N] |

|

| When asserted (low) the port timeouts are |

|

| |||

|

|

|

| enabled. When |

|

| ||

|

|

|

| disabled. |

|

|

|

|

|

|

|

| This signal is active low. |

|

|

|

|

|

|

|

| An external pull down resistor (e.g. 4k7 Ω) is |

|

| ||

|

|

|

| recommended on this pin so to enable the |

|

| ||

|

|

|

| watchdog timers. |

|

|

|

|

|

|

|

|

|

| |||

STAT_MUX_OUT(5) | In |

| Power on reset value which determines the | CMOS3V3 |

| |||

[maps to |

|

| initial timeout value. The following values |

|

| |||

POR_SEL_TIMEOUT0_N] |

|

| determine which timeout is selected at power |

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Preliminary |

|

| 43 |

|