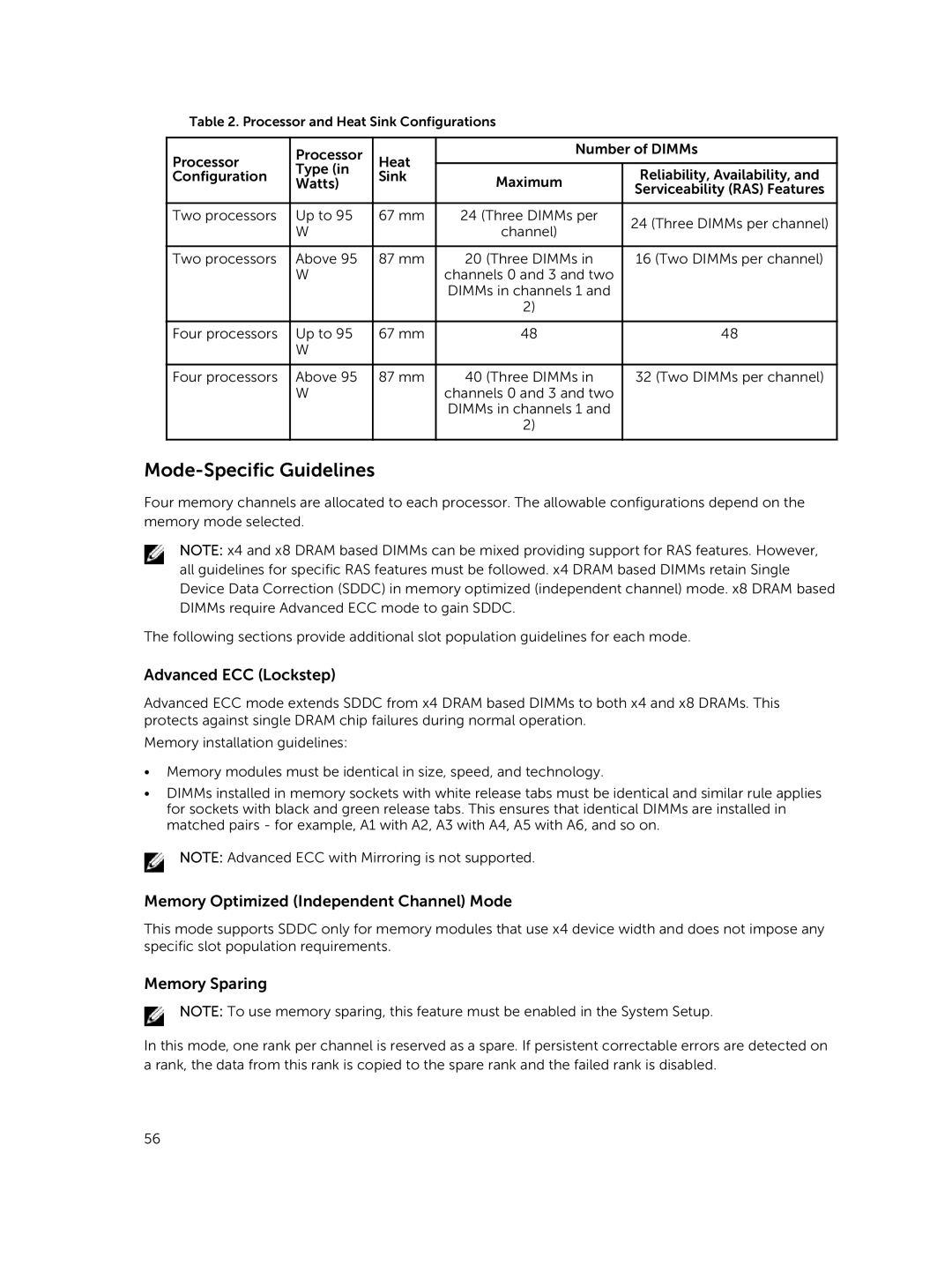

Table 2. Processor and Heat Sink Configurations

Processor | Processor | Heat | Number of DIMMs | ||

|

| ||||

Configuration | Type (in | Sink | Maximum | Reliability, Availability, and | |

Watts) | |||||

|

| Serviceability (RAS) Features | |||

|

|

|

| ||

|

|

|

|

| |

Two processors | Up to 95 | 67 mm | 24 (Three DIMMs per | 24 (Three DIMMs per channel) | |

| W |

| channel) | ||

|

|

| |||

|

|

|

|

| |

Two processors | Above 95 | 87 mm | 20 (Three DIMMs in | 16 (Two DIMMs per channel) | |

| W |

| channels 0 and 3 and two |

| |

|

|

| DIMMs in channels 1 and |

| |

|

|

| 2) |

| |

|

|

|

|

| |

Four processors | Up to 95 | 67 mm | 48 | 48 | |

| W |

|

|

| |

|

|

|

|

| |

Four processors | Above 95 | 87 mm | 40 (Three DIMMs in | 32 (Two DIMMs per channel) | |

| W |

| channels 0 and 3 and two |

| |

|

|

| DIMMs in channels 1 and |

| |

|

|

| 2) |

| |

|

|

|

|

| |

Mode-Specific Guidelines

Four memory channels are allocated to each processor. The allowable configurations depend on the memory mode selected.

NOTE: x4 and x8 DRAM based DIMMs can be mixed providing support for RAS features. However, all guidelines for specific RAS features must be followed. x4 DRAM based DIMMs retain Single Device Data Correction (SDDC) in memory optimized (independent channel) mode. x8 DRAM based DIMMs require Advanced ECC mode to gain SDDC.

The following sections provide additional slot population guidelines for each mode.

Advanced ECC (Lockstep)

Advanced ECC mode extends SDDC from x4 DRAM based DIMMs to both x4 and x8 DRAMs. This protects against single DRAM chip failures during normal operation.

Memory installation guidelines:

•Memory modules must be identical in size, speed, and technology.

•DIMMs installed in memory sockets with white release tabs must be identical and similar rule applies for sockets with black and green release tabs. This ensures that identical DIMMs are installed in matched pairs - for example, A1 with A2, A3 with A4, A5 with A6, and so on.

NOTE: Advanced ECC with Mirroring is not supported.

Memory Optimized (Independent Channel) Mode

This mode supports SDDC only for memory modules that use x4 device width and does not impose any specific slot population requirements.

Memory Sparing

NOTE: To use memory sparing, this feature must be enabled in the System Setup.

In this mode, one rank per channel is reserved as a spare. If persistent correctable errors are detected on a rank, the data from this rank is copied to the spare rank and the failed rank is disabled.

56