Hardware Information

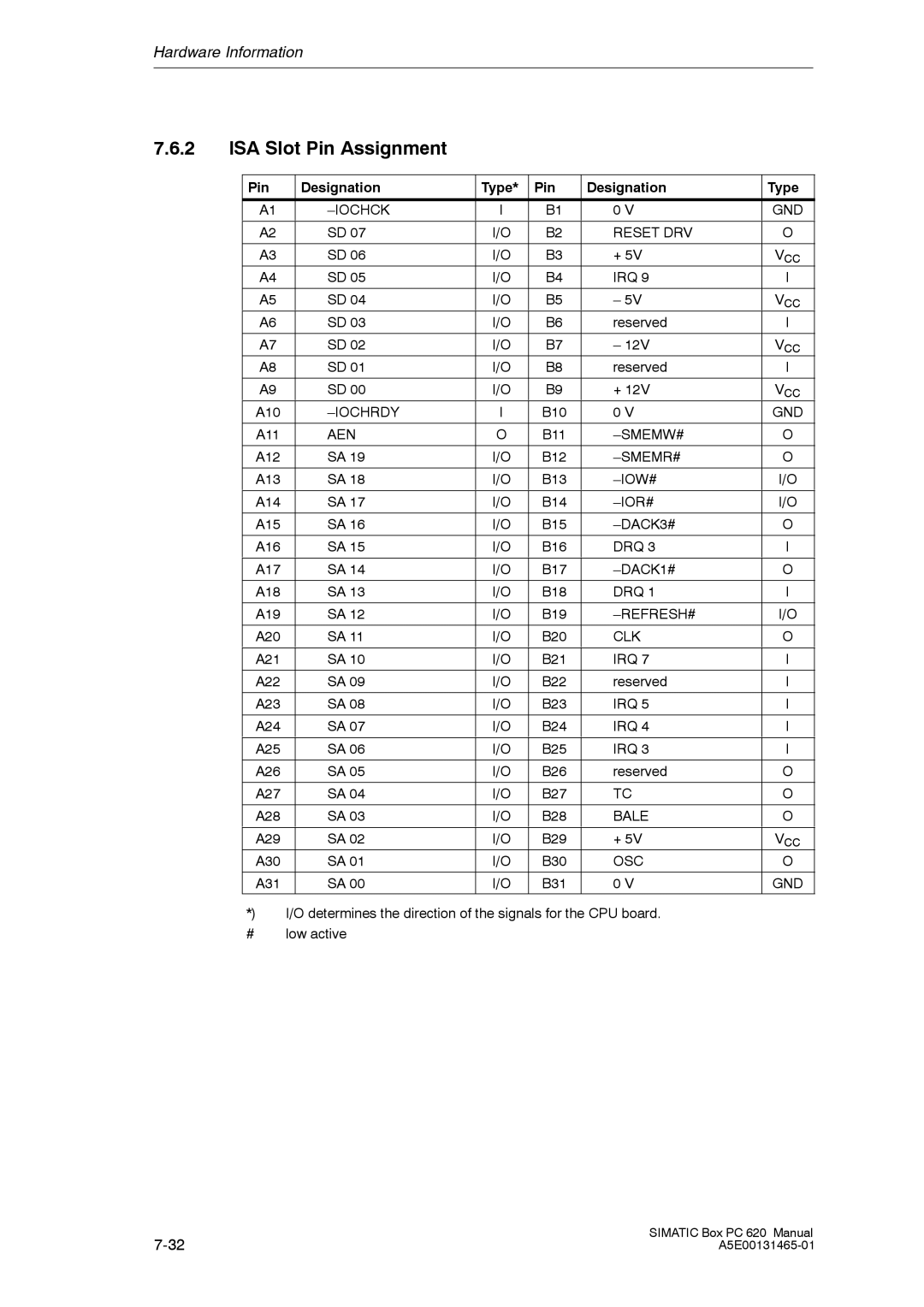

7.6.2ISA Slot Pin Assignment

Pin |

| Designation | Type* | Pin | Designation | Type |

|

|

|

|

|

|

|

A1 |

| I | B1 | 0 V | GND | |

|

|

|

|

|

|

|

A2 |

| SD 07 | I/O | B2 | RESET DRV | O |

|

|

|

|

|

|

|

A3 |

| SD 06 | I/O | B3 | + 5V | VCC |

A4 |

| SD 05 | I/O | B4 | IRQ 9 | I |

|

|

|

|

|

|

|

A5 |

| SD 04 | I/O | B5 | – 5V | VCC |

A6 |

| SD 03 | I/O | B6 | reserved | I |

|

|

|

|

|

|

|

A7 |

| SD 02 | I/O | B7 | – 12V | VCC |

A8 |

| SD 01 | I/O | B8 | reserved | I |

|

|

|

|

|

|

|

A9 |

| SD 00 | I/O | B9 | + 12V | VCC |

A10 |

| I | B10 | 0 V | GND | |

|

|

|

|

|

|

|

A11 |

| AEN | O | B11 | O | |

|

|

|

|

|

|

|

A12 |

| SA 19 | I/O | B12 | O | |

|

|

|

|

|

|

|

A13 |

| SA 18 | I/O | B13 | I/O | |

|

|

|

|

|

|

|

A14 |

| SA 17 | I/O | B14 | I/O | |

|

|

|

|

|

|

|

A15 |

| SA 16 | I/O | B15 | O | |

|

|

|

|

|

|

|

A16 |

| SA 15 | I/O | B16 | DRQ 3 | I |

|

|

|

|

|

|

|

A17 |

| SA 14 | I/O | B17 | O | |

|

|

|

|

|

|

|

A18 |

| SA 13 | I/O | B18 | DRQ 1 | I |

|

|

|

|

|

|

|

A19 |

| SA 12 | I/O | B19 | I/O | |

|

|

|

|

|

|

|

A20 |

| SA 11 | I/O | B20 | CLK | O |

|

|

|

|

|

|

|

A21 |

| SA 10 | I/O | B21 | IRQ 7 | I |

|

|

|

|

|

|

|

A22 |

| SA 09 | I/O | B22 | reserved | I |

|

|

|

|

|

|

|

A23 |

| SA 08 | I/O | B23 | IRQ 5 | I |

|

|

|

|

|

|

|

A24 |

| SA 07 | I/O | B24 | IRQ 4 | I |

|

|

|

|

|

|

|

A25 |

| SA 06 | I/O | B25 | IRQ 3 | I |

|

|

|

|

|

|

|

A26 |

| SA 05 | I/O | B26 | reserved | O |

|

|

|

|

|

|

|

A27 |

| SA 04 | I/O | B27 | TC | O |

|

|

|

|

|

|

|

A28 |

| SA 03 | I/O | B28 | BALE | O |

|

|

|

|

|

|

|

A29 |

| SA 02 | I/O | B29 | + 5V | VCC |

A30 |

| SA 01 | I/O | B30 | OSC | O |

|

|

|

|

|

|

|

A31 |

| SA 00 | I/O | B31 | 0 V | GND |

|

|

|

|

|

|

|

*) | I/O determines the direction of the signals for the CPU board. |

| ||||

#low active

SIMATIC Box PC 620 Manual | |