Hardware Information

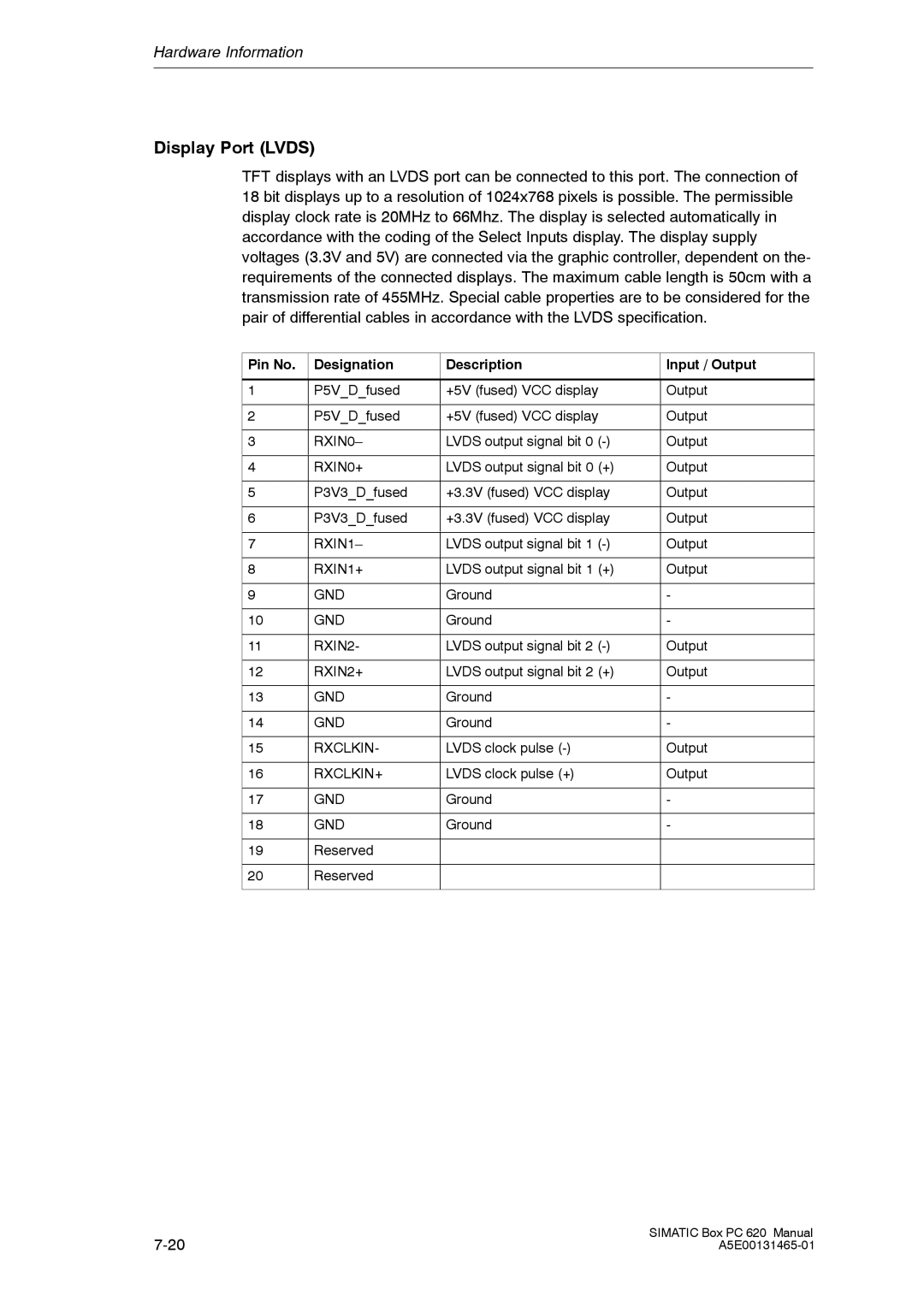

Display Port (LVDS)

TFT displays with an LVDS port can be connected to this port. The connection of 18 bit displays up to a resolution of 1024x768 pixels is possible. The permissible display clock rate is 20MHz to 66Mhz. The display is selected automatically in accordance with the coding of the Select Inputs display. The display supply voltages (3.3V and 5V) are connected via the graphic controller, dependent on the- requirements of the connected displays. The maximum cable length is 50cm with a transmission rate of 455MHz. Special cable properties are to be considered for the pair of differential cables in accordance with the LVDS specification.

Pin No. | Designation | Description | Input / Output |

|

|

|

|

1 | P5V_D_fused | +5V (fused) VCC display | Output |

|

|

|

|

2 | P5V_D_fused | +5V (fused) VCC display | Output |

|

|

|

|

3 | RXIN0– | LVDS output signal bit 0 | Output |

|

|

|

|

4 | RXIN0+ | LVDS output signal bit 0 (+) | Output |

|

|

|

|

5 | P3V3_D_fused | +3.3V (fused) VCC display | Output |

|

|

|

|

6 | P3V3_D_fused | +3.3V (fused) VCC display | Output |

|

|

|

|

7 | RXIN1– | LVDS output signal bit 1 | Output |

|

|

|

|

8 | RXIN1+ | LVDS output signal bit 1 (+) | Output |

|

|

|

|

9 | GND | Ground | - |

|

|

|

|

10 | GND | Ground | - |

|

|

|

|

11 | RXIN2- | LVDS output signal bit 2 | Output |

|

|

|

|

12 | RXIN2+ | LVDS output signal bit 2 (+) | Output |

|

|

|

|

13 | GND | Ground | - |

|

|

|

|

14 | GND | Ground | - |

|

|

|

|

15 | RXCLKIN- | LVDS clock pulse | Output |

|

|

|

|

16 | RXCLKIN+ | LVDS clock pulse (+) | Output |

|

|

|

|

17 | GND | Ground | - |

|

|

|

|

18 | GND | Ground | - |

|

|

|

|

19 | Reserved |

|

|

|

|

|

|

20 | Reserved |

|

|

|

|

|

|

SIMATIC Box PC 620 Manual | |