KS152JB Universal Communications Controller Technical Specifications

GMOD.0 (PR) - Protocol - If set SDLC protocols with NRZI encoding, zero bit insertion, and SDLC flags are used. If cleared, CSMA/CD link access with Manchester encoding is used.

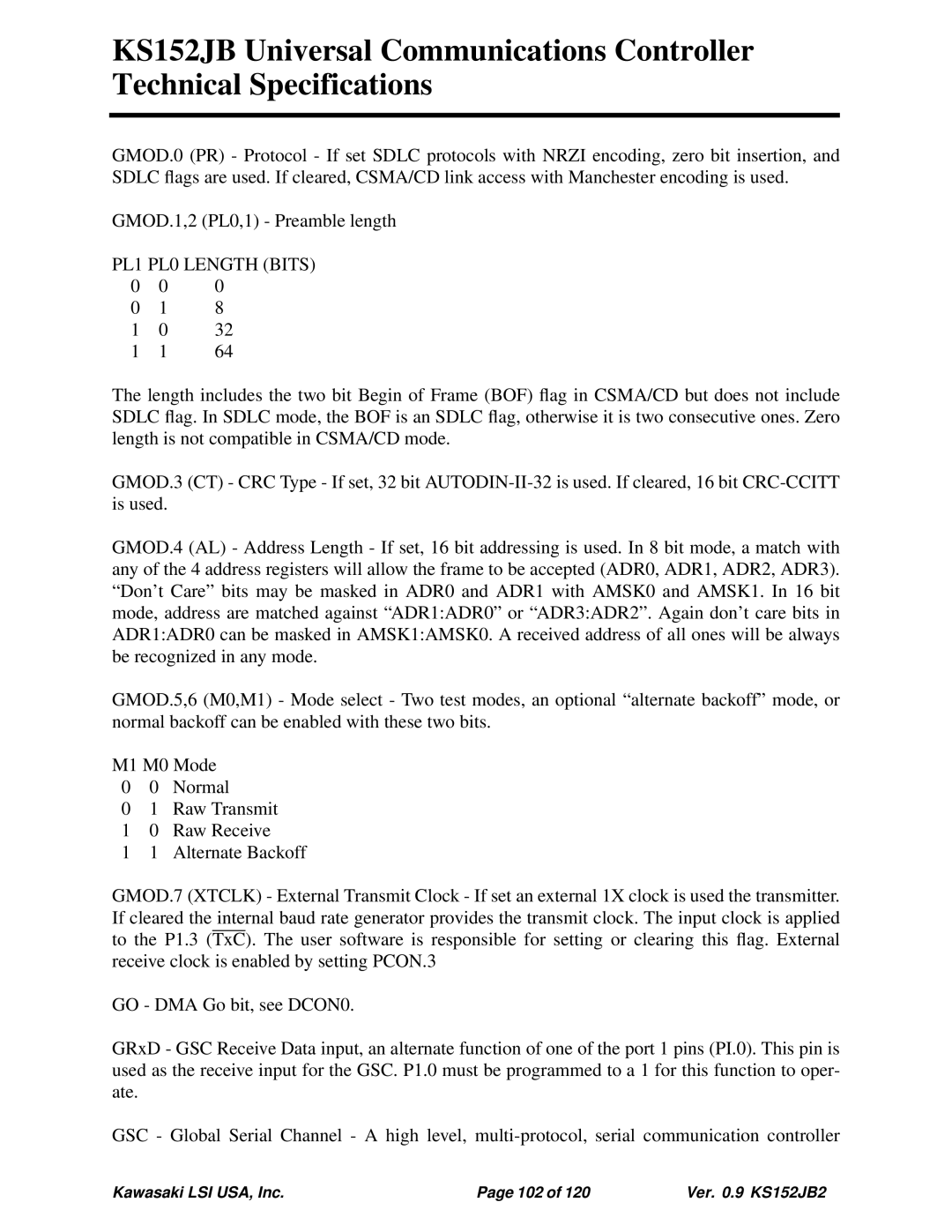

GMOD.1,2 (PL0,1) - Preamble length

PL1 PL0 LENGTH (BITS)

0 | 0 | 0 |

0 | 1 | 8 |

1 | 0 | 32 |

1 | 1 | 64 |

The length includes the two bit Begin of Frame (BOF) flag in CSMA/CD but does not include SDLC flag. In SDLC mode, the BOF is an SDLC flag, otherwise it is two consecutive ones. Zero length is not compatible in CSMA/CD mode.

GMOD.3 (CT) - CRC Type - If set, 32 bit

GMOD.4 (AL) - Address Length - If set, 16 bit addressing is used. In 8 bit mode, a match with any of the 4 address registers will allow the frame to be accepted (ADR0, ADR1, ADR2, ADR3). “Don’t Care” bits may be masked in ADR0 and ADR1 with AMSK0 and AMSK1. In 16 bit mode, address are matched against “ADR1:ADR0” or “ADR3:ADR2”. Again don’t care bits in ADR1:ADR0 can be masked in AMSK1:AMSK0. A received address of all ones will be always be recognized in any mode.

GMOD.5,6 (M0,M1) - Mode select - Two test modes, an optional “alternate backoff” mode, or normal backoff can be enabled with these two bits.

M1 M0 Mode

0 0 Normal

01 Raw Transmit

10 Raw Receive

1 1 Alternate Backoff

GMOD.7 (XTCLK) - External Transmit Clock - If set an external 1X clock is used the transmitter. If cleared the internal baud rate generator provides the transmit clock. The input clock is applied to the P1.3 (TxC). The user software is responsible for setting or clearing this flag. External receive clock is enabled by setting PCON.3

GO - DMA Go bit, see DCON0.

GRxD - GSC Receive Data input, an alternate function of one of the port 1 pins (PI.0). This pin is used as the receive input for the GSC. P1.0 must be programmed to a 1 for this function to oper- ate.

GSC - Global Serial Channel - A high level,

Kawasaki LSI USA, Inc. | Page 102 of 120 | Ver. 0.9 KS152JB2 |