KS152JB Universal Communications Controller Technical Specifications

P1.2 is programmed to a 1.

DM - DMA Mode, see DCON0

DMA - Direct Memory Access mode, see TSTAT.

DONE - DMA done bit, see DCON0.

DPH - Data Pointer High, an SFR that contains the high order byte of a general purpose pointer called the data pointer(DPTR).

DPL - Data Pointer Low, an SFR that contains the low order byte of the data pointer.

EDMA0 - Enable DMA Channel 0 interrupt, see IEN1.

EDMA1 - Enable DMA Channel 1 interrupt, see IEN1.

EGSRE - Enable GSC Receive Error interrupt, see IEN1.

EGSRV - Enable GSC Receive Valid interrupt, see IEN1.

EGSTE - Enable GSC Transmit Error interrupt, see IEN1.

EGSTV - Enable GSC Transmit Valid interrupt, see IEN1.

EOF - A general term used in serial communications. Eof stands for End Of Frame and signifies when the last bits of data are transmitted when using packetized data.

ES - Enable LSC service interrupt, see IE.

ET0 - Enable Timer 0 interrupt, see IE.

ET1 - Enable Timer 1 interrupt, see IE.

EX0 - Enable External interrupt 0, see IE.

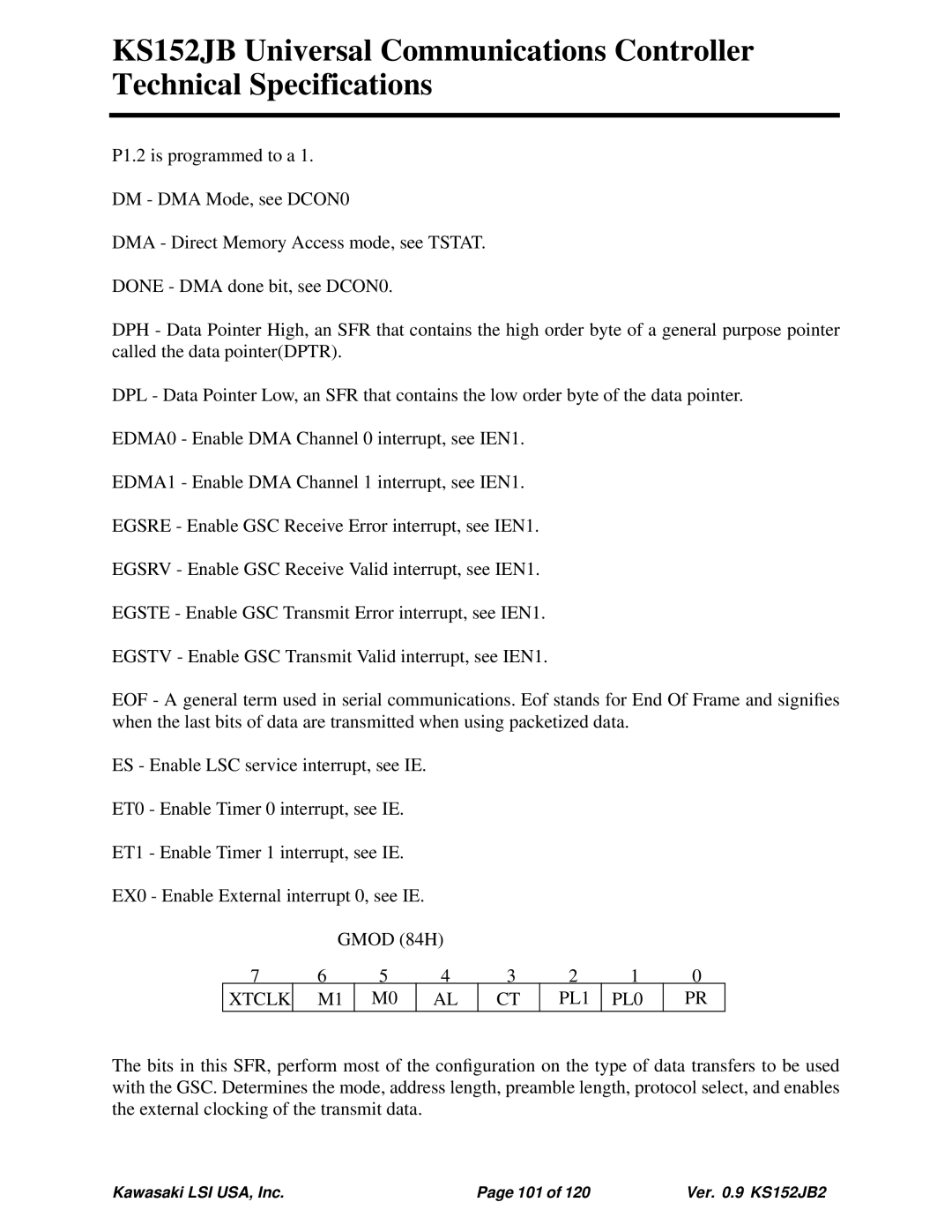

| GMOD (84H) |

|

|

|

| ||

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

XTCLK | M1 | M0 | AL | CT | PL1 | PL0 | PR |

The bits in this SFR, perform most of the configuration on the type of data transfers to be used with the GSC. Determines the mode, address length, preamble length, protocol select, and enables the external clocking of the transmit data.

Kawasaki LSI USA, Inc. | Page 101 of 120 | Ver. 0.9 KS152JB2 |