KS152JB Universal Communications Controller Technical Specifications

3.5.10 Receiver Clock Recovery

The receiver is always monitored at eight times the baud rate frequency, except when an external clock is used. When using an external clock the receiver is loaded during the clock cycle.

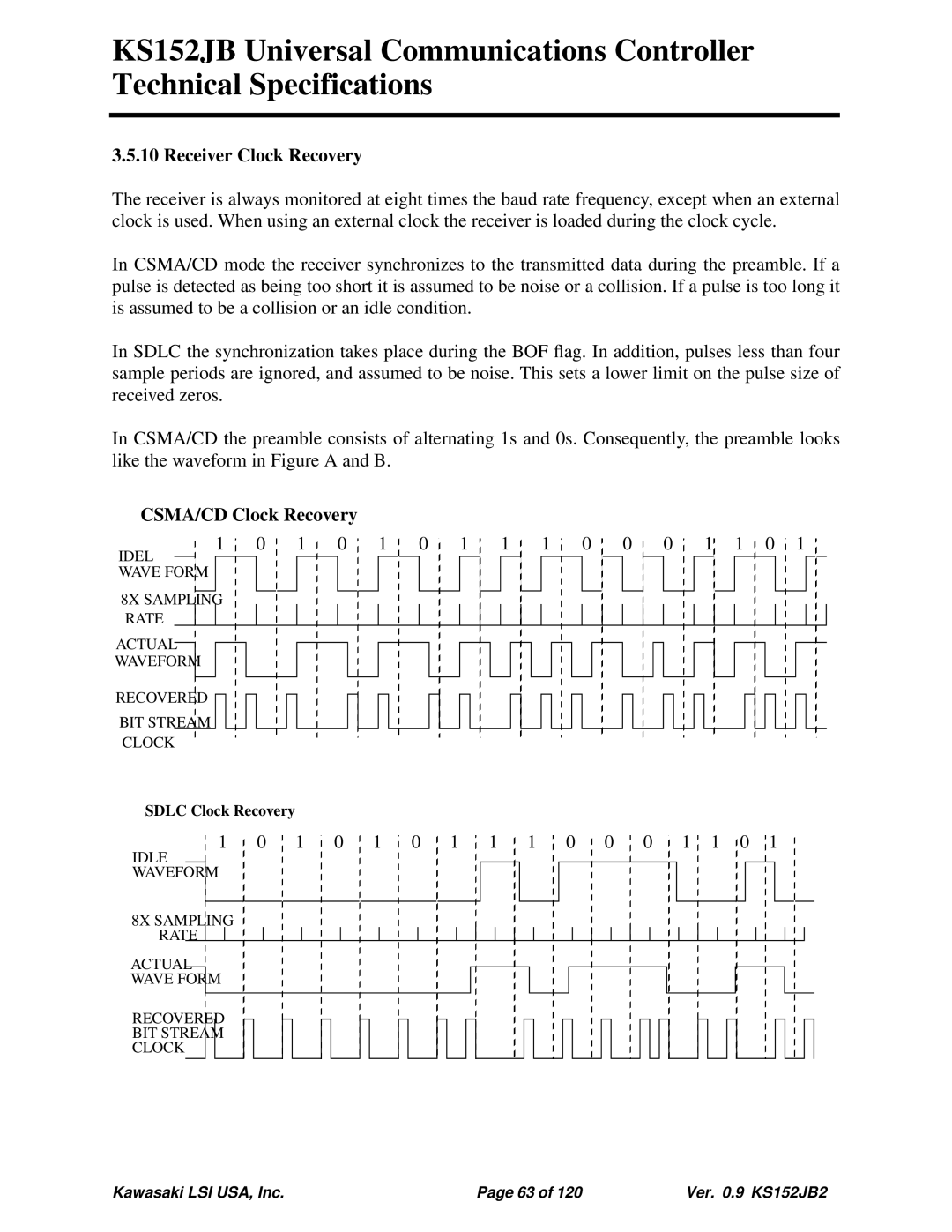

In CSMA/CD mode the receiver synchronizes to the transmitted data during the preamble. If a pulse is detected as being too short it is assumed to be noise or a collision. If a pulse is too long it is assumed to be a collision or an idle condition.

In SDLC the synchronization takes place during the BOF flag. In addition, pulses less than four sample periods are ignored, and assumed to be noise. This sets a lower limit on the pulse size of received zeros.

In CSMA/CD the preamble consists of alternating 1s and 0s. Consequently, the preamble looks like the waveform in Figure A and B.

CSMA/CD Clock Recovery

1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 |

IDEL

WAVE FORM

8X SAMPLING RATE

ACTUAL

WAVEFORM

RECOVERED

BIT STREAM

CLOCK

SDLC Clock Recovery

1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 |

IDLE

WAVEFORM

8X SAMPLING RATE ![]()

![]()

ACTUAL

WAVE FORM

RECOVERED

BIT STREAM

CLOCK

Kawasaki LSI USA, Inc. | Page 63 of 120 | Ver. 0.9 KS152JB2 |