KS152JB Universal Communications Controller Technical Specifications

It is recommended that user software should never write 1s to unimplemented bits in

The

5.1 GSC Transmitter Error Conditions

The GSC Transmitter section reports three kinds of error conditions:

TCDT - Transmitter Collision Detector

UR - Underrun in Transmit FIFO

NOACK - No Acknowledge

These bits reside in the TSTAT register. User software can read them, but only the GSC hardware can write to them. The GSC hardware will set them in response to the various error conditions that they represent. When the user software sets the TEN bit, the GSC hardware will at that time clear these flags. This is the only way these flags can be cleared.

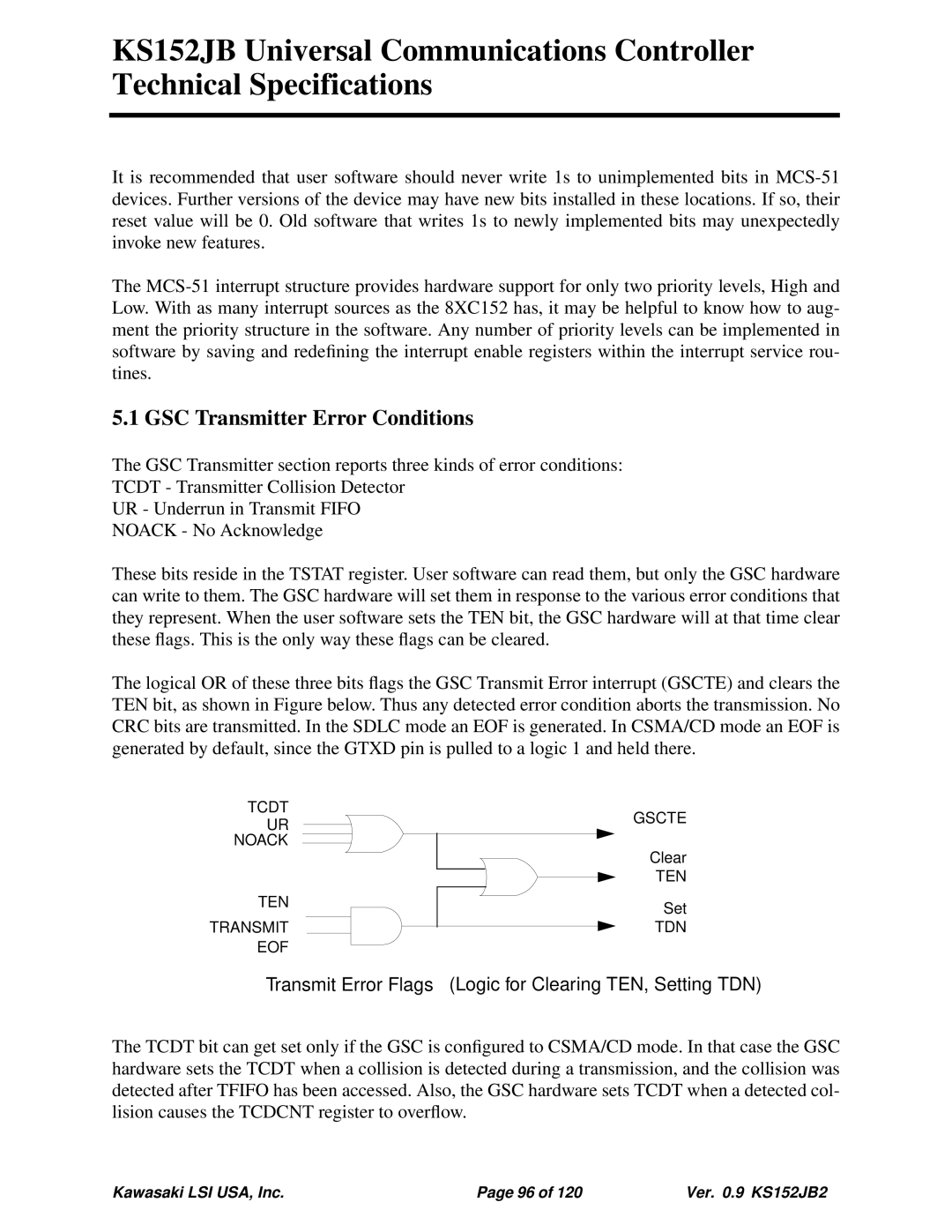

The logical OR of these three bits flags the GSC Transmit Error interrupt (GSCTE) and clears the TEN bit, as shown in Figure below. Thus any detected error condition aborts the transmission. No CRC bits are transmitted. In the SDLC mode an EOF is generated. In CSMA/CD mode an EOF is generated by default, since the GTXD pin is pulled to a logic 1 and held there.

TCDT

UR

NOACK

TEN

TRANSMIT EOF

GSCTE

Clear

TEN

Set

TDN

Transmit Error Flags (Logic for Clearing TEN, Setting TDN)

The TCDT bit can get set only if the GSC is configured to CSMA/CD mode. In that case the GSC hardware sets the TCDT when a collision is detected during a transmission, and the collision was detected after TFIFO has been accessed. Also, the GSC hardware sets TCDT when a detected col- lision causes the TCDCNT register to overflow.

Kawasaki LSI USA, Inc. | Page 96 of 120 | Ver. 0.9 KS152JB2 |